인텔이 2016년 이후 매 2년마다 새로운 미세화 공정을 적용하던 '틱톡 전략'을 6년만에 다른 방법으로 되살리겠다고 밝혔다.

매년 새 공정 적용 준비를 마쳐 자체 생산 프로세서는 물론 지난해 IDM 2.0 전략에 따라 다른 회사 제품 생산도 준비하겠다는 것이다. 이를 위해 일부 미세 공정 적용 시기를 앞당기고 오레곤 주 힐스보로 소재 '고든 무어 파크'에서 선행 기술을 시험하기 위한 시제품 생산도 진행한다.

인텔은 지난 2월 투자자 대상 브리핑에 이어 이달 11일(현지시간) 오레곤 주 힐스보로 소재 D1X 팹 개장을 앞두고 미국 현지 기자들을 대상으로 진행한 브리핑에서 이런 방침을 보다 명확히 밝혔다.

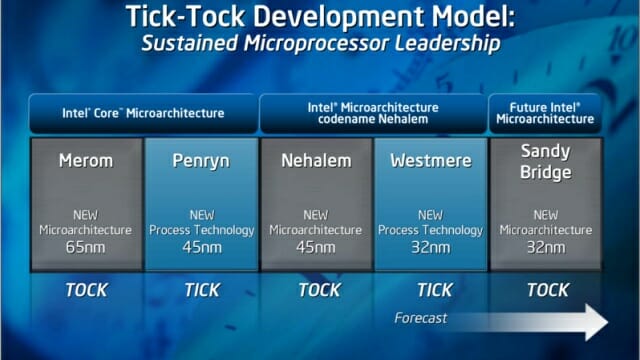

■ 공정-아키텍처 번갈아 개선한 '틱톡' 전략

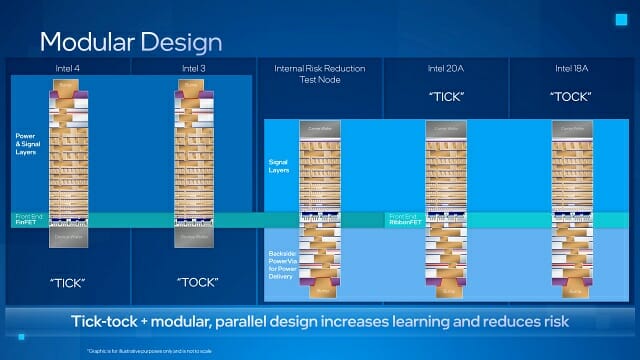

인텔은 첫 해에 공정을 미세화한 제품을 내놓는 '틱'(Tick), 그리고 이 공정을 바탕으로 다음 해에 새로운 아키텍처를 적용한 프로세서를 내놓는 '톡'(Tock) 전략을 2015년 6세대 코어 프로세서(스카이레이크)까지 적용했다.

10나노급 공정 전환에 어려움을 겪던 인텔은 2016년부터 P(제조공정)-A(아키텍처)-O(최적화) 전략을 내세웠다. 이 전략대로라면 늦어도 2018년에는 10나노급 프로세서가 나와야 했지만 10나노급 공정 지연은 계속됐다.

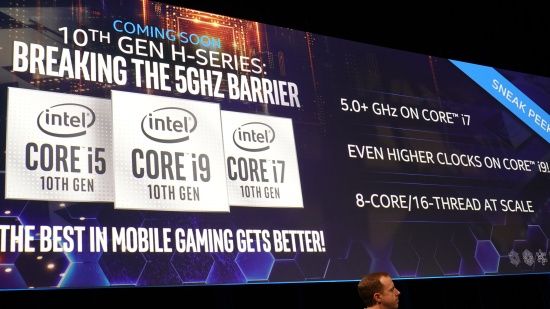

결국 데스크톱용 프로세서에서는 지난해 상반기까지(11세대 코어 프로세서, 로켓레이크), 노트북용 프로세서에도 2020년 상반기까지(10세대 코어 프로세서, 코멧레이크) 14나노 공정이 쓰였다.

■ 힐스보로 D1X 시설 브리핑서 '틱톡' 다시 등장

인텔은 11일 오레곤 주 힐스보로 D1X 반도체 생산 시설 공개를 앞두고 미국 현지 기자들을 대상으로 사전 브리핑을 진행하며 '틱톡'을 언급했다.

단 예전처럼 특정 해에 공정, 다음 해에 아키텍처 전환 등을 명시한 것은 아니다. 모듈화, 점진적, '틱톡' 유사를 내세워 매 해마다 새로운 공정 적용, 또는 개선된 아키텍처를 적용한 새 제품을 출시하겠다는 의미로 읽힌다.

인텔은 10나노급 공정 전환 당시 새 공정에 새로운 아키텍처를 적용해야 한다는 원칙을 고수하다 각종 신기술 도입에서 차질을 빚으며 경쟁사인 AMD의 추격을 허용했다.

2020년 하반기에는 10세대 코어 프로세서(아이스레이크)의 내부 구조를 14나노급으로 옮기고 데이터 입출력 관련 구조도 개선한 데스크톱용 11세대 코어 프로세서(로켓레이크)를 내놨다. 그러나 실제 성능 향상 폭은 기대에 미치지 못했다.

■ 선행 첨단 기술 검증 위한 시제품 생산 과정 추가

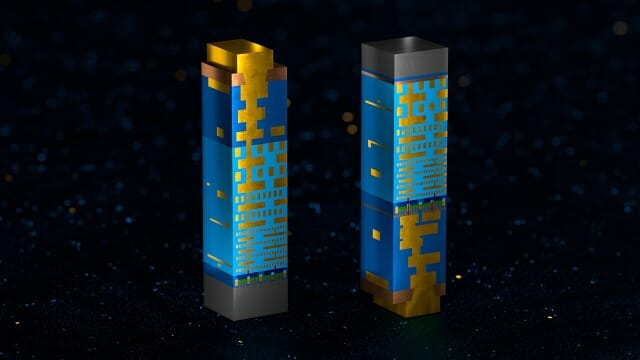

실제로 인텔은 2024년 출시할 프로세서 '애로우레이크'(Arrow Lake) 생산 공정에 세 가지 첨단 기술 투입을 공언해 왔다.

0.55 NA EUV(극자외선), 반도체 다이를 사이에 두고 위에는 트랜지스터 신호 전달층, 아래에는 전력 공급층을 두는 구조 '파워비아'(PowerVia), 새로운 트랜지스터 구조인 '리본펫'(RibbonFET) 등이 그것이다.

예정대로 제품 생산이 진행되려면 이 세가지 핵심 기술이 모두 차질없이 구현되어야 한다. 그러나 개발 과정에서 생기는 문제로 공정이 지연될 가능성도 배제할 수 없다.

인텔은 이를 위해 기존 3차원 핀펫 구조와 파워비아를 활용한 중간 단계 제품을 내부에서 생산하면서 공정 지연 등 문제점을 막겠다는 것이다.

■ "인텔 18A 공정 양산 준비, 2024년 하반기에 마친다"

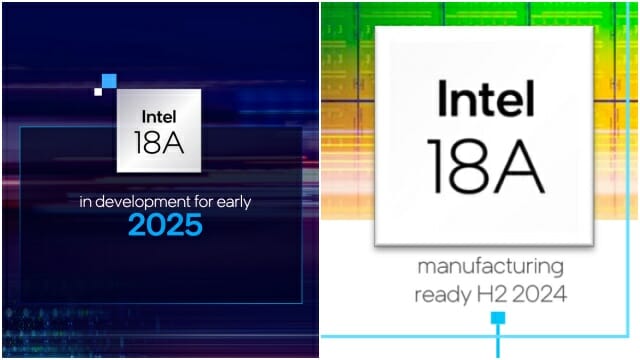

이날 인텔 발표에서 눈여겨 볼 점은 또 있다. 인텔이 '옹스트롬'(Ångström, 1A=0.1nm)급 미세 공정이라고 평가한 '인텔 18A' 전환을 약 반 년 가량 앞당긴다고 밝힌 것이다.

인텔은 지난 해 7월 말 생산 공정과 패키징 관련 로드맵을 공개하는 행사인 '액셀러레이티드'를 통해 "2025년 초를 목표로 초미세 공정인 '인텔 18A'를 개발중"이라고 밝힌 바 있다.

그러나 이날 인텔은 '인텔 18A' 공정 양산 준비 완료 시기를 2024년 하반기로 앞당긴다고 설명했다. 이 공정을 이용해 생산되는 프로세서로는 '루나레이크'(Lunar Lake)가 꼽힌다.

인텔은 지난 2월 중순 투자자·분석가 대상 행사 '인베스터 미팅 2022'에서도 같은 취지의 발표를 한 바 있다. 2024년 3분기 중 양산 채비를 마친 뒤 4분기 말(연말)에 루나레이크 출시가 예상된다.

■ 공정은 오레곤, 아키텍처는 하이파로 이분화

향후 인텔의 공정과 반도체 생산 기술 등 연구 개발은 미국 오레곤 주 힐스보로 소재 고든 무어 파크가 전담할 것으로 보인다.

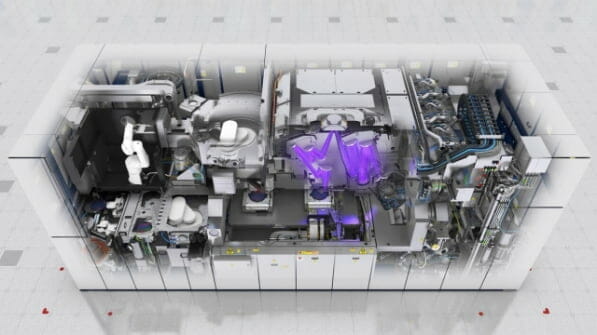

특히 개구율 0.55NA(렌즈수차)급 ASML 장비인 '트윈스캔 EXE:5200'은 장비 부피가 기존 EUV 장비 대비 부피가 커서 도입할 수 있는 곳이 한정적이다.

관련기사

- 인텔, 미국 오레곤 주 힐스보로 생산시설 확장 개장2022.04.12

- 인텔은 왜 독일에 새 반도체 공장 지을까2022.03.16

- 인텔, 2024년까지 출시할 PC 프로세서 로드맵 공개2022.02.21

- 인텔, 차세대 ASML 극자외선 EUV 장비 도입2022.01.19

반면 P(퍼포먼스, 고성능) 코어와 E(에피션트, 고효율) 코어를 조합한 하이브리드 코어 등 아키텍처 관련 기술은 이스라엘 하이파 소재 연구소에서 전담할 것으로 보인다.

이 연구소에는 1989년 인텔에 입사해 2017년부터 멜라녹스에 근무했던 실로미트 바이스가 지난 해 7월부터 인텔로 돌아와 근무중이다.