하이닉스(대표 권오철)가 40나노미터(nm)급 2기가비트(Gb) DDR3 D램을 8단으로 쌓아 세계최대 용량의 단일 적층 D램칩 개발에 성공했다고 9일 발표했다.

기존의 와이어 본딩(Wire bonding) 기술로는 패키지 크기 증가와 전기적 특성 저하로 인해 16기가비트 D램 단일 패키지로 제작할 수 없었다. 이의 구현을 위해서는 20나노 초반급 공정기술을 적용해야 한다.

하이닉스는 이 기술에 대해 “메모리·시스템반도체·이미지센서 등 여러 가지 기능을 담당하는 칩들이 통합되는 추세를 보이는 가운데 기술력을 미리 확보했다는 점에서 의미가 크다”고 설명했다.

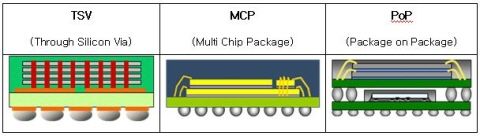

메모리반도체를 서로 연결하는 패키징을 위해서는 지금까지 금형배선(와이어본딩) 방식이 주로 사용돼 왔다. 하지만 최근 들어 적은 면적 안에 많은 수의 반도체를 집적하기 위한 방식으로 관통전극(Thyrough Silicon Via·TSV)적층방식이 등장해 적용되기 시작했다.

일반적으로 와이어본딩방식을 통해 반도체를 평면에 늘어놓고 배선을 통해 연결하는 반면 TSV는 배선 없이 칩들을 수직으로 쌓아올리고 전극이 관통하게 하는 방식이다. 일반적으로 TSV 적층기술은 일반적으로 멀티칩패키지(MCP)나 패키지온패키지(PoP)와 같은 와이어본딩 사용 방식에 비해 2배 이상 적층할 수 있다. 또 동작속도는 50%이상, 소비전력은 40% 가량 줄어드는 효과를 내는 것으로 보고되고 있다.

하이닉스는 TSV 기술을 활용해 제작한 16Gb D램을 모듈형태로 제작하면 최대 64기가바이트(GB)의 고용량을 구현할 수 있어 서버·워크스테이션 등 대용량 메모리 수요에 적합하다고 설명했다.

관련기사

- 하이닉스 올해 투자 D램 분야 70% 비중2011.03.09

- 삼성전자, 차세대 DDR4 D램 시대 ‘연다’2011.03.09

- 하이닉스, 세계최초 30나노 4Gb D램 개발2011.03.09

- KT, 1분기 영업익 4827억원...전년비 29.9%↓2026.05.12

홍성주 하이닉스 연구소장은 “TSV 기술을 이용한 고용량 메모리 제조기술은 앞으로 2~3년 내에 메모리 산업 핵심기술이 될 것”이라며 “고용량과 융복합화에 맞는 메모리 솔루션 기반을 구축했다는 점에 의의가 있다”고 밝혔다.

하이닉스는 2013년 이후 상용화될 것으로 예상되는 64GB 모듈 양산을 준비중이며, 기존 모바일 D램보다 8배 빠른 와이드I/O TSV기술도 개발 중이다.