대만 파운드리 TSMC가 차세대 AI 반도체 시장을 목표로 첨담 패키징 기술을 고도화하고 있어 주목된다. AI 반도체가 점차 고성능·대면적화되는 추세에 맞춰, HBM4(6세대 고대역폭메모리)를 80개까지 탑재한 제품을 고안해낸 것으로 파악됐다.

12일 업계에 따르면 TSMC는 지난달 말 미국 텍사스주에서 열린 'ECTC 2025(전자부품기술학회)'에서 초대형 AI 반도체를 위한 '시스템온웨이퍼(SoW-X)'의 구체적인 구조를 발표했다.

16개 컴퓨팅 칩에 80개 HBM 연결…기존 대비 전성비 1.7배 향상

SoW-X는 TSMC가 오는 2027년 양산을 목표로 하고 있는 차세대 패키징 기술이다. GPU·CPU 등 고성능 시스템반도체와 HBM을 집적한 AI 반도체 분야에 적용될 예정이다.

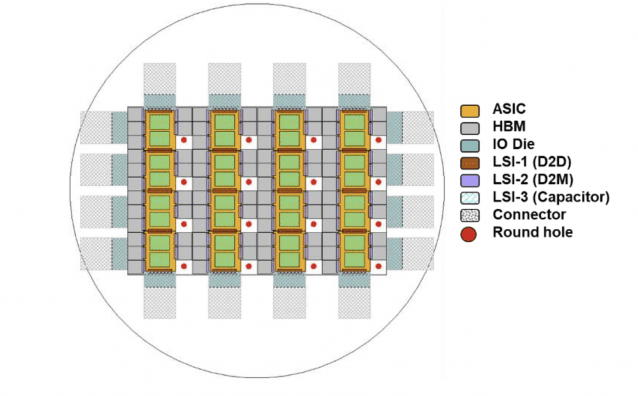

SoW-X는 기존 패키징 공정에서 쓰이던 기판(PCB)나 실리콘 인터포저(칩과 기판 사이에 삽입되는 얇은 막)를 사용하지 않고, 메모리 및 시스템반도체를 웨이퍼 상에서 직접 연결하는 것이 핵심이다.

각 칩의 연결은 칩 하단에 형성된 미세한 구리 재배선층(RDL)이 담당한다. 이 때 RDL은 칩 외부로 확장되는데, TSMC에서는 이를 InFO(Integrated Fan-Out)라고 부른다.

SoW-X는 웨이퍼 전체를 활용하기 때문에 초대형 AI 반도체 제작이 가능하다. TSMC가 발표한 자료에 따르면, SoW-X는 최대 16개의 고성능 컴퓨팅 칩, 80개의 HBM4 모듈을 집적했다. 이로 인해 총 메모리 용량은 3.75TB(테라바이트), 대역폭은 160TB/s에 이른다.

또한 SoW-X는 동일한 수의 컴퓨팅 칩을 사용하는 기존 AI 반도체 클러스터에 비해 전력 소비량은 17% 줄어들었으며, 46% 향상된 성능을 제공할 수 있다.

TSMC는 "SoW-X는 각 칩 간의 뛰어난 연결성과 낮은 소비 전력으로 기존 AI 반도체 클러스터 대비 와트(W)당 전체 성능이 1.7배 가량 개선됐다"며 "훨씬 더 많은 시스템반도체와 HBM을 통합해 시스템 전력 효율성이 향상되며, 기존 기판 연결의 어려움도 제거할 수 있다"고 설명했다.

HPC·AI 시장 목표…"수요 당장 많지 않다" 지적도

TSMC는 SoW-X를 업계 표준을 능가하는 혁신적인 기술 플랫폼으로 평가하며, 차세대 고성능 컴퓨팅 및 AI 산업을 공략하겠다고 밝혔다.

다만 SoW-X 기술이 AI 메모리 시장에 미칠 여파가 당장은 크지 않다는 지적도 제기된다. HBM 탑재량이 80개로 매우 많지만, 지금 당장은 초대형 AI 반도체에 대한 수요가 제한적이라는 이유에서다.

관련기사

- TSMC 손 잡은 SK하이닉스, HBM4 로직 다이 비용 압박↑2025.05.30

- "TSMC, 1.6나노 웨이퍼 가격 2나노 대비 50% 인상 예정"2025.06.05

- TSMC, AI칩 수요 견조 재확인…삼성·SK, HBM 사업 성장세 '쾌청'2025.04.21

- TSMC, CoWoS에 '플럭스리스 본딩' 적용 추진…AI칩 대형화에 대응2025.03.06

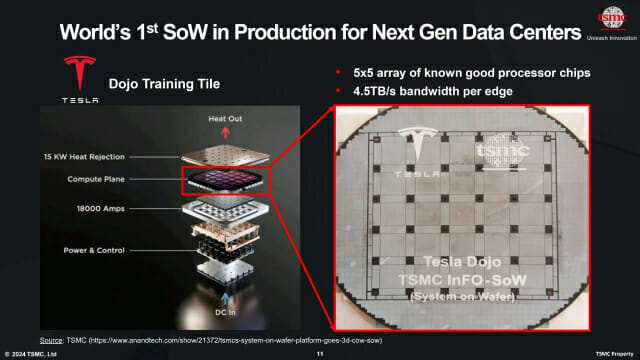

실제로 SoW-X의 이전 세대로 지난 2020년 도입된 SoW는 테슬라·세레브라스 등 소수의 고객사만이 양산에 채택한 바 있다.

반도체 업계 관계자는 "테슬라의 슈퍼컴퓨팅 '도조(Dojo)' 전용 칩인 'D1'처럼, SoW-X는 완전한 커스터마이즈 칩을 위한 기술로서 니치 마켓에 부합한다"며 "워낙 많은 칩이 탑재되고 기술적인 난이도도 높아, 대중적인 AI 반도체 패키징 기술을 당장 대체하기는 어려울 것"이라고 말했다.