대만 주요 파운드리 TSMC가 첨단 패키징 기술인 '플럭스리스(Fluxless)' 본딩을 적용하는 방안을 추진 중이다. 지난해부터 관련 장비를 도입해 평가를 진행해 온 것으로 파악됐다. AI 산업의 발달로 패키징 크기가 점차 확대되면서, 기술 전환의 필요성이 높아졌다는 분석이 제기된다.

6일 업계에 따르면 TSMC는 2.5D 패키징에 플럭스리스 본딩을 적용하기 위한 공정 평가를 진행하고 있다.

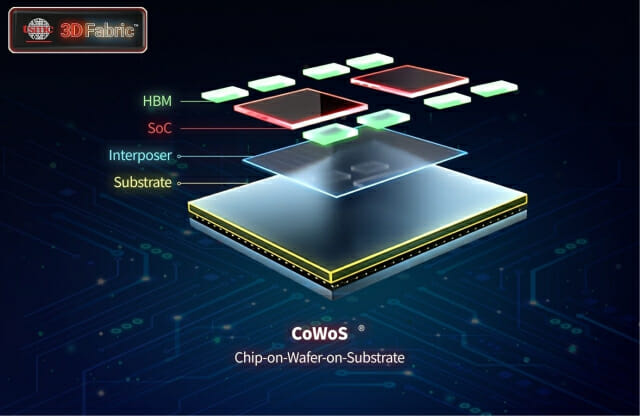

그간 TSMC는 2.5D 패키징을 'CoWoS(Chip-on-Wafer-on-Substrate)'라는 브랜드명으로 자체 개발해 왔다.

TSMC는 지난해 2곳 이상의 해외 주요 반도체 장비업체로부터 플럭스리스 본딩 장비를 들여와, CoWos에 양산 적용하기 위한 평가를 진행하고 있다. 나아가 올 상반기에도 또 다른 협력사와 추가적인 평가를 시작할 예정인 것으로 파악됐다.

2.5D 패키징은 칩과 기판 사이에 넓다란 실리콘 인터포저 위에 반도체 다이(Die)를 수평 배치하는 기술이다. 기판만을 활용하는 기존 2D 패키징에 비해 회로를 더 밀도있게 연결할 수 있다. 특히 HBM과 고성능 GPU를 연결하는 데이터센터용 AI 가속기 분야에서 CoWoS에 대한 수요가 높다.

TSMC는 그간 CoWoS에 플럭스(Flux)를 활용해 왔다. 플럭스는 칩과 인터포저를 연결하는 미세한 범프의 접착력을 높이고, 접합 품질을 떨어트리는 산화막을 방지하는 역할을 맡고 있다.

그러나 CoWoS는 점차 플럭스를 쓰기 어려워지는 환경으로 진화하고 있다. 플럭스는 범프의 접합이 끝난 뒤 제거(세정)돼야 하는데, 인터포저 크기가 커지면 가운데에 묻은 플럭스를 완전히 제거하기가 어렵기 때문이다. 플럭스가 잔존하면 칩 신뢰성이 저해될 수 있다.

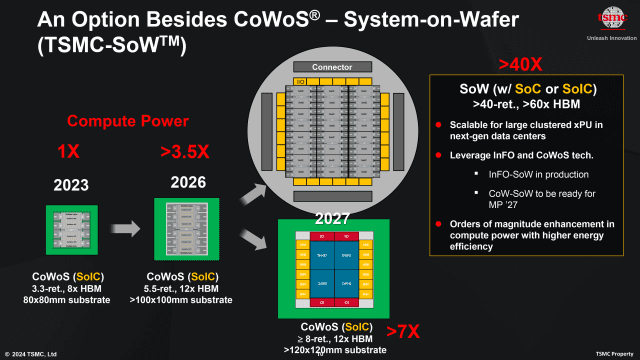

실제로 TSMC의 CoWoS 패키징 내 인터포저 크기는 지난 2023년 기준 80x80mm 수준이었다. 레티클(포토마스크; 반도체 회로를 새기기 위한 원판) 대비 약 3.3배 크다.

TSMC는 이를 오는 2026년 100x100mm(레티클 대비 5.5배)까지 확대할 계획이다. 2027년에는 120x120mm(레티클 대비 8배) 수준으로 커진다. AI 가속기에 요구되는 컴퓨팅 성능이 높아질수록 더 많은 칩을 내장해야 하기 때문에, 인터포저의 크기도 덩달아 커지는 추세다.

플럭스리스 본딩은 이 문제를 해결할 수 있는 대안으로 꼽힌다. 플럭스리스는 플럭스를 사용하지 않고 범프의 산화막을 제거하는 기술이다. 때문에 해외 주요 반도체 장비기업들이 관련 기술 개발에 주력하고 있다.

관련기사

- 차세대 HBM용 본딩 고민하는 삼성전자, '플럭스리스' 평가 돌입2025.03.04

- "韓 고객사 관심 많다"…K&S, HBM4용 '플럭스리스' TC 본더 장비 파란 예고2025.02.23

- TSMC, 美에 145조원 추가 투자...트럼프 "놀라운 일"2025.03.04

- TSMC, 삼성電 반도체 또 넘었다...작년 年매출액 128조원 '폭풍 질주'2025.01.10

TSMC도 향후 CoWoS에 플럭스리스 본딩을 적용하는 방안을 적극 검토하는 분위기다. 특히 TSMC는 지난해 CoWoS 수율 향상에 난항을 겪은 바 있어, 플럭스리스를 비롯한 대안 기술에 관심을 기울일 수 밖에 없다는 게 업계의 전언이다.

반도체 업계 관계자는 "현재 TSMC는 플럭스리스 본더를 소량 들여와 연구개발(R&D) 단계에서 평가를 진행하는 중"이라며 "올해까지 테스트가 마무리 될 것으로 보고 있다"고 설명했다.