인텔이 반도체 제조 공정 우위를 되찾기 위해 올 하반기부터 적용할 예정이었던 신기술 2종 투입을 연기했다.

새 트랜지스터 구조 '리본펫'(RibbonFET), 반도체 후면 전력 전달 기술 '파워비아'(PowerVIA) 적용 시점을 올 하반기에서 내년 상반기로 반 년 가량 연기했다.

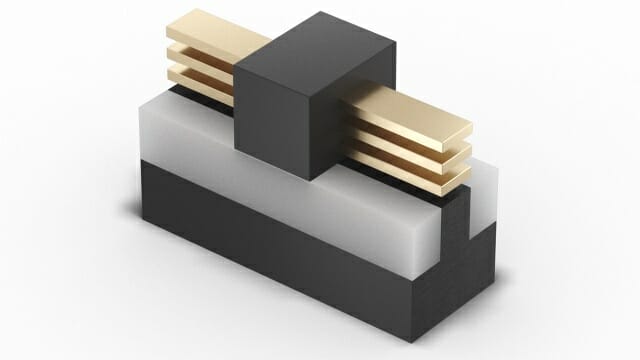

리본펫은 트랜지스터를 흐르는 전류를 보다 매끄럽게 제어할 수 있도록 트랜지스터 사이를 연결하는 핀의 넓이를 넓히는 방식으로 만들어진다. 삼성전자도 3nm 공정에 유사한 기술인 '게이트올어라운드'(GAA)를 적용하고 있다.

파워비아는 신호와 전력을 공급하던 배선이 섞여 있던 구조에서 벗어나 트랜지스터 위쪽에서는 신호만 주고 받고 아래쪽에 전력을 공급하는 배선을 둔다. 이를 가리켜 '웨이퍼 후면 전력 전달 기술'이라고 부른다.

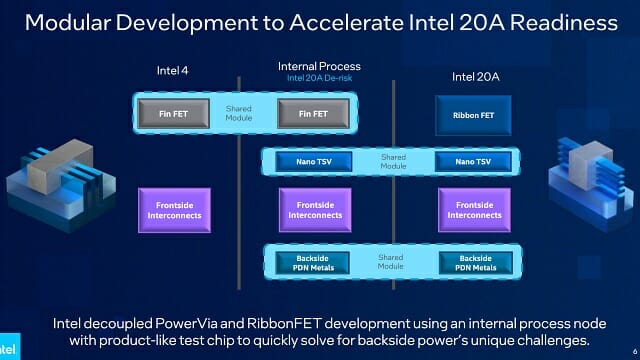

인텔은 올 하반기부터 가동될 2나노급 공정인 인텔 20A(Intel 20A) 투입을 목표로 리본펫 트랜지스터와 파워비아 기술을 연구해 왔다. 지난 해 6월에는 대만 TSMC보다 2년 앞서 파워비아 기술 구현 성공했다고 밝히기도 했다.

그러나 인텔은 1일(미국 현지시간) 실적발표에서 "내년 양산될 '팬서레이크'(Panther Lake)는 인텔 18A 공정과 함께 리본펫·파워비아 기술을 적용할 첫 마이크로프로세서가 될 것"이라고 설명했다. 양대 기술 적용 시점을 반 년에서 1년 가량 미룬 것이다.

이날 팻 겔싱어 인텔 CEO는 "인텔 18A 공정을 반도체 생산에 활용할 수 있는 제품설계킷(PDK)를 지난 달 출시했으며 올 연말까지 양산 준비를 마치고 계획대로 내년 상반기부터 양산에 들어갈 것"이라고 밝혔다.

이어 "PC용 팬서레이크 시제품은 윈도 운영체제 부팅에 성공했으며 리본펫, 파워비아와 첨단 패키징 기술을 활용하는 첫 마이크로프로세서가 될 것"이라고 설명했다.

관련기사

- 인텔, 13/14세대 코어 프로세서 보증기간 2년 연장2024.08.02

- 인텔, 사상 최대 규모 1만 5천명 감원 예고...주가도 급락2024.08.02

- 인텔, 2분기 2.2조원 적자... 매출도 전년比 1% 감소2024.08.02

- 인텔, 파운드리 부문 나가 찬드라세카란 CCO 선임2024.07.26

인텔이 올 하반기 투입할 데스크톱PC용 차세대 프로세서 '애로우레이크'(Arrow Lake)는 인텔 20A 공정에서 생산된다.

인텔 관계자는 "인텔 20A 관련 상세 내용은 이를 적용한 제품인 '애로우레이크' 출시 시점에 공개할 것"이라고 답변했다.