삼성전자가 최신 스마트워치에 탑재될 웨어러블 AP(애플리케이션 프로세서) 엑시노스 W1000을 공식 행사에서 처음으로 언급했다. 해당 칩은 3나노미터(nm) 공정과 '빅-리틀'이라는 새로운 아키텍처를 적용한 것이 특징이다.

삼성전자는 10일(현지시간) 프랑스 파리에서 '갤럭시 언팩' 행사를 열고 최신형 스마트워치인 '갤럭시 워치7·워치 울트라'를 공개했다.

'갤럭시 워치7'은 갤럭시 워치 시리즈 중 최초로 ‘최종당화산물(AGEs) 지표)’ 측정을 제공하는 것이 특징이다. 갤럭시 워치 라인업에 새롭게 추가된 ‘갤럭시 워치 울트라'의 경우 티타늄 프레임 적용, 10ATM 방수 기능, 절전 모드서 최대 100시간 사용 등 성능을 극대화했다.

두 개의 워치 제품은 모두 삼성전자가 자체 개발한 최첨단 웨어러블 AP 엑시노스 W1000을 탑재하고 있다. 엑시노스 W1000의 적용처가 공개된 것은 이번 행사가 처음이다.

엑시노스 W1000은 삼성전자의 GAA(게이트-올-어라운드) 기술이 적용된 2세대 3나노(SF3) 공정을 기반으로 한다. GAA는 전류가 흐르는 채널 4개면을 게이트(Gate)가 둘러 싼 트랜지스터 구조다. 채널 3개면을 감싸던 기존 핀펫(FinFET) 구조 대비 데이터 처리 성능 및 효율성이 높다.

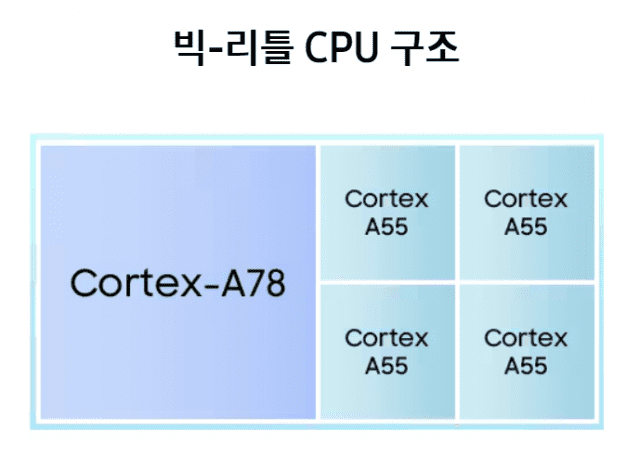

이날 발표를 진행한 톰 쿨리모어 삼성전자 제품 및 영업 담당은 "두 워치 제품의 뛰어난 성능은 하드웨어와 소프트웨어의 강력한 최적화를 통해 이뤄졌다"며 "3나노 공정과 '빅-리틀(Big-Little)' 아키텍처를 통해 CPU 성능이 이전 세대 대비 3배 빨라졌다"고 강조했다.

아키텍처는 반도체의 하드웨어와 소프트웨어간의 구동 방식을 표준화한 일종의 설계도다.

빅-리틀 구조는 삼성전자의 웨어러블 프로세서에는 처음 적용된 구조다. 고성능 작업은 빅코어를 통해, 그렇지 않은 작업은 리틀코어를 통해 분산 작업하는 기술을 뜻한다.

관련기사

- 갤럭시워치7에 수면 무호흡증 감지 기능…이전 모델은?2024.07.10

- 삼성전자, '엑시노스 2500' 수율 개선 총력…하반기 '갤S25' 명운 갈린다2024.06.21

- 삼성전자, 3나노 '웨어러블 AP' 공개...갤워치7 탑재2024.07.03

- 삼성 갤럭시워치7 울트라, 이렇게 나온다2024.05.25

엑시노스 W1000의 경우 Arm 코어텍스-A78 칩 1개를 빅코어로 두고 있다. 리틀코어인 Arm 코어텍스-A55는 전작 대비 2배 늘린 4개를 집적했다. 삼성전자는 "이를 통해 전작 대비 싱글코어는 3.4배, 멀티코어는 3.7배 높은 성능을 제공한다"고 설명했다.

한편 엑시노스 W1000에는 첨단 패키징 기술인 FO-PLP(팬아웃-패널레벨패키징)도 적용됐다. FO-PLP는 기존 웨이퍼보다 넓은 사각형 패널을 사용해 생산성을 높일 수 있다. 또한 PMIC(전력관리반도체)와 메모리를 결합해 칩 크기를 줄이는 ePOP(임베디드 패키지 온 패키지)도 적용됐다.