인텔이 반도체 웨이퍼 후면으로 전력을 전달하는 새로운 구조 '파워비아'(PowerVia) 구현에 성공했다고 밝혔다.

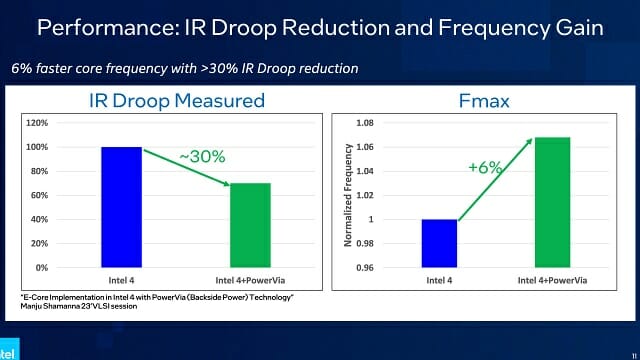

인텔은 인텔 4 공정에서 생산한 저전력·고효율 E(에피션트)코어 8개에 파워비아 기술을 적용한 결과 보다 적은 전력으로 높은 주파수를 얻을 수 있고 전력 소모도 줄었다고 설명했다.

반도체 후면으로 전력을 전달하는 기술은 대만 TSMC도 2026년경 적용을 목표로 개발중이었다. 인텔은 파워비아 구현을 통해 첨단공정 리더십에 한 발 더 다가섰다.

■ 공정 미세화 따라 신호·전력 배선 분리 필요성 대두

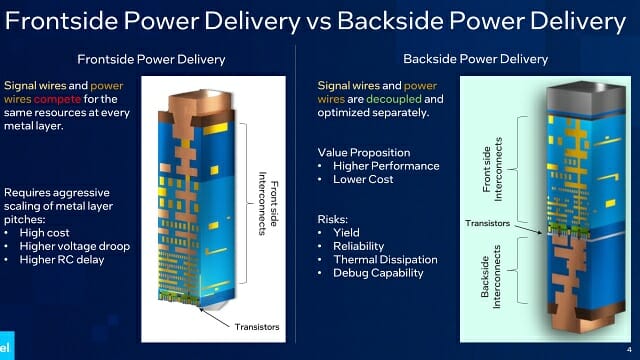

반도체 다이는 신호 뿐만 아니라 전력을 공급하는 배선이 반드시 필요하다. 현재 가장 널리 쓰이는 방식은 가장 아래에 트랜지스터를 두고 전력 배선을 가장 위에, 그 다음 신호를 전달하는 배선을 두는 것이다.

그러나 공정 미세화에 따라 점점 더 가는 배선을 연결할 필요성이 생겼다. 문제는 신호와 전력 배선이 한데 얽히며 점점 더 복잡해지고 더 높은 전압을 공급해야 해 효율성이 떨어진다는 것이다.

파워비아는 신호와 전력을 공급하던 배선이 섞여 있던 구조에서 벗어나 트랜지스터 위쪽에서는 신호만 주고 받고 아래쪽에 전력을 공급하는 배선을 두는 것이다. 이를 가리켜 '웨이퍼 후면 전력 전달 기술'이라고 부른다.

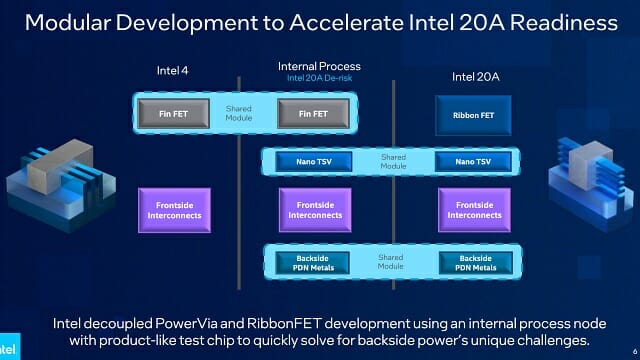

■ 파워비아·EUV 기술 모듈화로 위험 회피

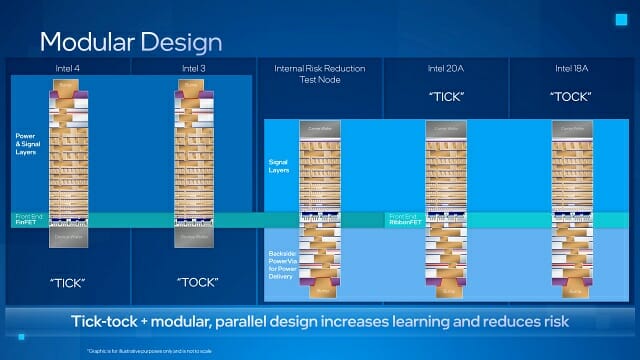

인텔은 14→10나노급 공정 전환시 한꺼번에 새로운 기술을 모두 투입하려다 제품 생산 시기를 놓치는 뼈아픈 실기를 범했다.

인텔은 2024년 인텔 20A·18A 공정 일환으로 투입될 파워비아 기술 적용을 앞두고 기존 3차원 핀펫 구조와 파워비아를 활용한 중간 단계 제품을 내부에서 시험 생산하는 방식을 택했다. 이를 통해 신기술 개발시 생길 수 있는 위험을 줄였다.

인텔은 올 하반기 출시될 차세대 코어 프로세서 '메테오레이크'(Meteor Lake)에 투입되는 E(에피션트)코어 8개를 인텔 4 공정에서 생산한 다음 이 반도체에 파워비아 기술을 적용했다. 이 반도체에는 '블루스카이 크릭'(Blue Sky Creek)이라는 이름이 붙었다.

■ "기존 공정 대비 작동 클록 높이면서 전력 소모 줄여"

인텔은 "블루스카이 크릭은 반도체 내 구역의 90%를 유효하게 활용하면서 공급되는 전압이 떨어지는 'IR 전력 드룹'을 30% 이상 줄였다. 또 같은 전압으로 기존 대비 6% 더 높은 작동 클록을 얻는 데 성공했다"고 설명했다.

또 "파워비아 기술의 수율은 대량 생산이 가능한 수준이며 기존 공정 대비 트랜지스터의 특성과 안정성 기준, 발열 기준도 충족했다"고 밝혔다.

전력 배선을 반도체 후면으로 옮길 경우 반도체 내부의 문제를 찾는 디버그 과정도 달라진다. 인텔은 "블루스카이 크릭 칩 안에 '부활절 달걀'처럼 문제를 일으키는 회로를 숨긴 후 디버깅 팀에 문제 해결을 요청한 결과 문제 없이 이를 찾아냈다"고 설명했다.

■ "내년 가동되는 인텔 20A·18A 공정부터 파워비아 적용"

웨이퍼 후면 전력 전달 기술은 반도체 전력 소모를 줄이고 효율을 높이기 위해 반드시 필요하다. 대만 TSMC는 오는 2026년 2나노급(N2P) 공정부터 이 기술을 적용한다고 밝힌 바 있다.

관련기사

- [컴퓨텍스 2023] 차세대 인텔 코어 프로세서, AI로 효율성 ↑2023.05.30

- 인텔 "16비트 없는 순수 64비트 명령어 체계 만들자" 제안2023.05.24

- 인텔, 마이크로소프트와 협력해 윈도11 AI 고도화2023.05.24

- 인텔, ISC 2023에서 HPC 관련 협업 발표2023.05.23

인텔은 TSMC보다 2년 앞선 내년부터 인텔 20A·18A 등 공정에 파워비아 기술을 투입할 예정이다. 또 해당 공정을 이용하는 IFS(인텔 파운드리 서비스) 고객사도 파워비아 기술을 활용할 수 있다고 밝혔다.

인텔은 오는 11일부터 16일까지 일본 교토에서 진행되는 VLSI 심포지엄을 통해 파워비아 기술 구현과 관련된 논문 두 편도 공개할 예정이다.