가장 중요한 것은 생태계입니다. 협력업체 없는 삼성 파운드리는 불가능합니다. 삼성전자는 파트너와 절대 경쟁하지 않습니다. 파트너와 함께 생태계를 구축하고, 고객을 지원합니다. 삼성전자는 현재 17개의 EDA(전자 설계 자동화) 파트너와 2천370개의 DM(설계 방법론)을 확보하고 있습니다. 삼성 파운드리 기술을 탑재한 IP(지식 재산)는 3천300개에 달합니다. - 박재홍 삼성전자 파운드리 사업부 부사장.

우리 일상은 상상 이상의 더 많은 방식으로 연결되고 있습니다. 앞으로 5년 후에는 페타플롭(초당 1천조번의 연산처리) 시대를 넘어 엑사플롭(초당 100경의 연산처리)의 시대가 열리게 될 것입니다. 1천억개 이상의 지능형 기기가 서로 연결되고, 이는 인공지능의 발전과 함께 엄청난 컴퓨팅 성능을 요구하게 될 것입니다. 다시말해 전체 산업에 엄청난 성장 기회가 오게 될 것입니다. - 라자 코두리 인텔 수석부사장.

삼성전자가 파운드리 사업의 최근 성과와 향후 전략을 소개하는 '삼성 파운드리 SAFE 포럼 코리아 2020' 행사를 개최했다.

지난 29일부터 온라인으로 진행 중인 이번 포럼에는 ARM, 케이던스, 시놉시스, 앤시스, 멘토·지멘스 비즈니스 등 주요 반도체 업체들이 참석해 파운드리 시장의 기술 동향과 삼성 파운드리와의 협력 방안을 논의해 주목을 받았다. 특히, 라자 코두리 인텔 수석 부사장이 SAFE 포럼 기조연설에 나서면서 관련 업계의 관심이 더욱 집중됐다.

박재홍 삼성전자 파운드리 사업부 부사장은 이날 포럼에서 "삼성전자는 과거 14나노미터 공정부터 시작해 3나노미터 공정까지 노드 전환의 이점을 극대화하는 기술의 혁신을 이뤘다"며 "각 노드별로 PPA(Power Performance Area)를 계속 발전시켰고, 일례로 새로운 노드인 5LPP(Low Power Performance)는 5LPE(Low Power Early) 대비 5%의 성능 향상과 10%의 전력 절감을 이뤄냈다"고 기술 개발 현황을 소개했다.

이어 "4LPP도 마찬가지로 기존 4LPE 대비 5%의 성능 향상과 10%의 전력 절감을 달성, 이는 GAA(Gate All Around) 이전 최고의 PPA를 가진 5번째 EUV(극자외선) 노드"라며 "중요한 것은 같은 노드의 브랜치(회로를 구성하는 단일 소자)는 디자인 및 IP(설계자산)를 공유한다는 것으로, 예컨대 8LPA는 10나노미터 공정 노드와 이전의 8나노미터 공정 노드의 IP를 재사용할 수 있다. 삼성전자는 매년 10·8·7·5·4나노미터 공정을 새로 소개하며, 모두 평균적으로 이전 노드 대비 10%의 속도 증가, 로직(회로) 영역의 24% 감소, 17%의 전력 절감을 이뤄냈다"고 강조했다.

삼성전자가 파운드리 시장 1위 도약을 위해 준비 중인 비장의 무기 'GAA(게이트 올 어라운드)'와 더불어 여타 기술의 최신 개발 동향도 소개했다.

박재홍 부사장은 "GAA 트랜지스터를 적용한 새로운 기술 노드는 예정대로 수율과 성능이 개발, 2022년에 양산할 예정"이라며 "3나노미터 GAA 노드는 4나노미터 이후의 새로운 기술로, 이는 세계 최초의 GAA 노드이며 짧은 채널 효과 개선 및 낮은 VDD(전원전압)에서의 높은 성능을 갖는 GAA 나노 시트 트랜지스터다. (삼성전자의) GAA는 핀펫(finFET)과 비교해 공칭 전압 또는 낮은 VDD에서 조차 25~40%의 전력 절감과 10~15%의 속도 증가를 이뤘다"고 강조했다.

또 "고성능 컴퓨팅이 중요해지면서 데이터센터를 위한 성능 플랫폼, CPU·GPU(중앙처리장치·그래픽처리장치), 머신러닝·AI(인공지능)가 점점 더 중요해지고 있다"며 "삼성전자는 PCIe Gen6, D2D(Die-to-Die), 225G SerDes(직렬·병렬 변환기)와 HBM3 PHY(가용 물리계층)는 14나노미터부터 4나노미터 노드까지 새롭게 개발했거나 개발할 계획"이라고 전했다.

이어 "저비용 고대역폭 솔루션 2.5D RDL 패키지부터 고대역폭 솔루션 I-Cube, 3D TSV(실리콘 관통 전극) 기반으로 짧은 메모리 액세스 지연시간과 소형 폼팩터를 가능하게 하는 X-Cube 솔루션 등 고객의 필요에 따라 선택할 수 있는 패키지 솔루션의 종류도 다양하게 보유하고 있다"며 "2.5 RDL과 X-Cube는 양산 준비가 완료됐고, I-Cube(8X HBM)과 X/I-Cube는 내년 말까지 양산 준비가 완료될 예정이다. X/I-Cube는 X-Cube와 I-Cube를 통합해 짧은 메모리 액세스 지연 시간과 높은 D램 대역폭을 제공한다"고 덧붙였다.

초미세공정 기술의 성숙도를 높이기 위한 최적화에 대해서는 자신감을 내비쳤다.

박 부사장은 "각 기술 노드의 PPA 장점은 공정 기술로만 이룰 수 없고, 기술 차원이 점점 작아질수록 DTCO(Design Technology Co-Optimization)가 매우 중요해진다"며 "삼성전자는 전통적인 방식의 피치(회로 선폭)를 줄임으로써 스케일링(미세화)을 달성할 수 있었다. 7나노미터부터 5나노미터, 4나노미터까지 삼성전자는 DTCO를 최적화함으로써 셀의 높이를 243나노미터부터 200나노미터로 낮출 수 있었다"고 설명했다.

나아가 "그러나 DTCO에 의해 끊임없이 증가하는 저항은 삼성전자가 극복해야할 과제"라며 "또 EM(전자의 이동 현상)은 와이어(배선)와 비아(홀)의 점점 커지는 저항을 극복해야할 또다른 기술적 도전으로, 이에 삼성전자는 설계 컨텍스트 인식 전자파 방법론부터 열 인식 전자파 방법론, 통계 전자파 방법론 및 셀 전자파에 대한 화이트박스 확인을 개발했다. 이를 활용하면 칩셋 설계가 더 쉽고, 설계의 속도와 전력을 개선할 수 있다"고 강조했다.

아울러 "삼성 파운드리 솔루션은 플랫폼 방식을 채택해 EDA, IP, DSP(디자인 솔루션 파트너), 클라우드, 공정, 제조, 패키지를 원스탑솔루션으로써 고객의 생각을 현실화하고 있다"며 "삼성 파운드리 플랫폼은 시스템 수준의 솔루션이다. 삼성전자는 HPC(고성능 컴퓨팅), 모바일, 5G, 오토모티브, IoT(사물인터넷)을 포함하는 다양한 응용을 타깃으로 하고 있다"고 덧붙였다.

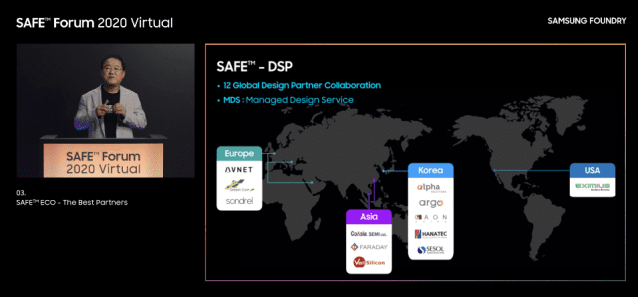

파운드리 생태계를 확장하기 위한 신규 프로그램과 그간의 성과도 공유했다.

박 부사장은 "올해부터 IP 품질 관리 프로그램인 SAFE-QCP를 시작, 이를 통해 IP 설계 품질과 실리콘 검증에 대한 정보를 제공받을 수 있다"며 "EDA와 관련해서는 EDA 툴의 검증 프로그램인 SAFE QEDA를 시작, 특히 SAFE 클라우드 디자인 플랫폼인 SAFE-CDP를 통해서는 멀리 있는 파트너와 협력해야 하는 경우, 기능적인 설계 환경에 즉각 접근할 수 있어 매우 유용하다"고 전했다.

나아가 "12개의 DSP는 높은 수준의 설계 서비스를 제공, 올해 새롭게 셋업한 MDS(Malware Detection system)는 삼성 파운드리가 설계 서비스의 성공적인 실행을 보증하기 위한 서비스"라며 "또 9개의 OSAT(외주 반도체 패키지 테스트) 패키지 파트너와 삼성 파운드리의 실리콘으로 검증된 16개의 패키지 플랫폼도 보유하고 있다"고 소개했다.

아울러 "삼성 파운드리는 파트너와 절대 경쟁하지 않는다. 파트너와 긴밀하게 협력함으로써 SAFE는 매년 성장하고 있다"며 "현재 17개의 EDA 파트너, 작년 대비 1.4배 증가한 2천370개의 DM을 확보했으며, 삼성 파운드리 기술을 탑재한 IP가 현재 3천300개로 50% 이상 증가했다. SAFE IP는 굉장히 확장, 45나노미터부터 3나노미터까지 3천300개의 IP 타이틀을 보유하고 있다"고 강조했다.

라자 코두리 인텔 수석부사장은 '1000X More Compute for AI by 2025(AI를 위한 1000배 컴퓨팅)'이라는 주제 발표를 통해 최근 인공지능 기술의 발전으로 주목받는 컴퓨팅 시장의 동향을 소개했다.

라자 코두리 수석부사장은 "오늘날의 컴퓨팅 환경은 전기처럼 모든 사람이 접속할 수 있는 것을 요구하고, 향후 5년 안에는 엄청나게 많은 컴퓨팅 파워를 필요하게 될 것"이라며 "앞으로 1천억개 이상의 지능형 기기가 서로 연결될 것으로 예상되는 가운데 이러한 인텔리전스는 엄청난 양의 컴퓨팅을 요구해 무어의 법칙보다 훨씬 더 가파른 궤적을 남기게 될 것"이라고 전했다.

이어 "AI 발전의 주요 혁신 중 하나는 데이터를 활용해 인텔리전스를 구축하는 것이지만, 이는 엄청난 양의 데이터를 생성하고 있고, 이를 분석하고 이해하기 위한 과정에서도 더 많은 데이터 생성이 이뤄지고 있어 결국 더 많은 컴퓨팅 파워가 필요하게 된다"며 "이에 메모리 계층 구조의 모든 수준에서 더 많은 용량과 대역폭이 필요하고, 대기 시간을 줄이면서 센서와 엣지에서 생성되는 기하급수적인 궤도를 따라가기 위한 네트워크 대역폭 역시 필요한 상황"이라고 덧붙였다.

나아가 "이로 인해 우리 일상은 상상 이상의 더 많은 방식으로 연결돼 앞으로 5년 후에는 페타플롭 시대를 넘어 엑사플롭의 시대가 열리게 될 것"이라며 "가까운 장래에 수백만 개의 센서가 그것을 작동시키는 극한의 엣지에서 컴퓨팅 스펙트럼을 확장하는 것을 보게 될 것"이라고 예측했다.

인공지능의 확산으로 급격히 증가하는 데이터를 빠르게 처리하기 위해 필요한 혁신 기술의 방향성도 제시했다.

라자 코두리 수석부사장은 "메모리 대역폭의 효율성은 AI 시대의 기존 메모리 기술 솔루션과 함께 요구되며, 이를 위해서는 메모리 전력을 지금보다 5~10배 가량 줄여야한다"며 "엣지가 수십억개의 센서에서 수집된 막대한 데이터를 빠르게 수집·처리하기 위해 클라우드로 모든 데이터를 이동하는 것은 불가능한 이야기로, 엣지 자체에서 데이터를 처리하는 방법을 찾아야하고, 이에 엣지에서의 컴퓨팅이 천배 이상 증가할 필요가 있다"고 전했다.

또 "컴퓨팅 분야에서 수천배의 (성능) 증가를 달성하기 위해서는 각 이해 관계자가 자신의 경로를 제공해야한다. 예컨대 메모리는 높은 메모리 밀도를 갖추면서 동시에 저전력으로 동작해야하고, 성능은 4배 이상 높아져야한다"며 "대역폭의 효율성 개선을 위해 인터커넥트의 성능도 4배 이상 높아져야한다. 그래야 더 빠른 네트워크 데이터 전송과 더 짧은 지연 시간이 가능해진다"고 설명했다.

차세대 컴퓨팅을 위한 최근의 기술 개발 동향도 공유됐다.

관련기사

- 삼성 "내년 상반기 반도체 턴어라운드 가능성 높다"2020.10.29

- 내년 파운드리 시장 더 뜨겁다...올해 대비 4.24% 성장2020.10.23

- 칩스앤미디어, '제2회 삼성 세이프 포럼' 참가2020.10.20

- TSMC·퀄컴 추격하는 삼성, 내년 초미세 공정으로 승부2020.10.05

라자 코두리 수석부사장은 "인텔은 파운드리, IP, EDA, 재료, 과학 및 장비 제조 전반에 걸쳐 중요한 기술 전문가와 경영진을 보유하고 있다"며 "인텔은 나노미터 측면에서의 차원 확장으로, 트랜지스터 동작이 발생하는 영역에서 원자의 수 또는 원자 밀도를 추적하는 것을 통해 앞으로 더 많은 트랜지스터 밀도 스케일링이 가능할 것으로 보고 있다"고 전했다.

이어 "핀펫(FinFET) 아키텍처 자체에 대해 적어도 3배 더 많은 밀도 확장이 가능하다고 본다. 예컨대 나노 와이어를 통해 2배 가량의 밀도 스케일링을 얻을 수 있고, 이러한 실험은 이미 랩에서 진행되고 있다"며 "인텔은 또한 리소그래피 스캐너의 레티클 한계를 극복하는 매우 큰 효과적인 다이를 만들 수 있다고 본다. 일례로 인텔의 Chiplet(프로세서 패키지 내 분리된 실리콘 구조) 기술은 단순한 제조 플랫폼 이상의 중요한 투자다. 반도체 산업은 첨단 패키징을 통해 앞으로 칩셋 설계에 대한 접근 방식을 근본적으로 바꿀 수 있다고 본다"고 덧붙였다.