삼성전자가 기존 대비 소비전력을 25% 절감하고 데이터 읽기 시간을 절반으로 줄인 플래시메모리 내장형(임베디드 플래시) 로직 공정을 개발했다. 내년 하반기에는 이를 적용한 첫 상용화 제품인 스마트카드IC 양산에 나설 계획이다.

삼성전자는 업계 최초로 45나노 임베디드 플래시(embeded Flash 혹은 eFlash) 로직 공정을 개발하고 이를 적용한 스마트카드 IC 테스트 칩 개발에 성공했다고 15일 발표했다.

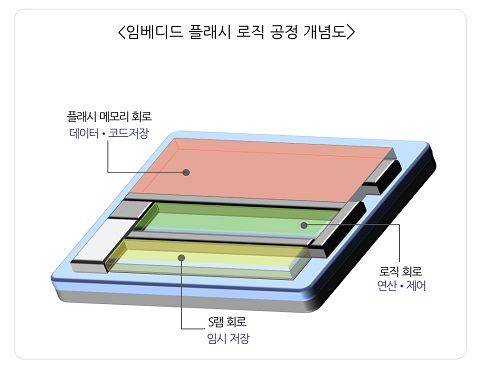

임베디드 플래시 로직 공정은 데이터를 제어하고 처리하는 시스템 반도체 회로안에 데이터를 기억하는 플래시메모리 회로를 구현하는 방식이다. 집적도와 전력효율을 높일 수 있어 가전, 모바일, 자동차 등 다양한 애플리케이션을 위한 제품에 적용된다.

이번에 개발에 성공한 45나노 스마트카드 IC 테스트 칩은 기존 80나노 공정 제품 대비 생산성이 높고 소모전력은 25% 절감하면서도 내부 플래시 메모리에서 데이터를 읽어 오는 시간(Random Access Time)을 50% 줄인 제품이다.

특히, 플래시 메모리 한 셀(Cell)당 최소 100만번 데이터 갱신(Endurance cycle)이 가능해 업계 최고 수준의 신뢰성을 확보했으며 상용화를 위한 내부 테스트도 마친 상태다.

삼성전자는 설계·공정의 최적화 작업과 신뢰성 있는 기관의 보안성 테스트를 거쳐 내년 하반기에 45나노 임베디드 플래시 공정을 적용한 스마트카드IC를 양산할 예정이다.

관련기사

- 삼성, 20나노급 4Gb 모바일 D램 양산2013.05.15

- 삼성전자, 10나노급 128Gb 낸드 양산 돌입2013.05.15

- 삼성전자, ‘엑시노스5 옥타’ 2분기 양산2013.05.15

- 삼성전자 14나노 핀펫 협력체계 구축2013.05.15

이를 통해 소비자 가전과 차량용 마이크로컨트롤러유닛(MCU) 제품 분야의 파운드리 및 주문형반도체(ASIC) 고객에 경쟁력 있는 솔루션을 제공한다는 계획이다.

김태훈 삼성전자 시스템LSI사업부 상무는 이번 45나노 임베디드 플래시 로직 공정은 스마트카드, NFC 등 다양한 보안 솔루션과 모바일 제품에 적용이 기대된다며 다양한 제품군에서 첨단 공정을 우선 적용해 종합 모바일 솔루션 공급자로서의 입지를 강화할 것이라고 밝혔다.