글로벌 프로그래머블 반도체(PLD) 설계 전문 업체 자일링스와 알테라가 타이완 TSMC와의 파운드리 협력관계를 종료하고 ASE와 SPIL 등으로 물량을 이전할 것이라는 관측이 나왔다.

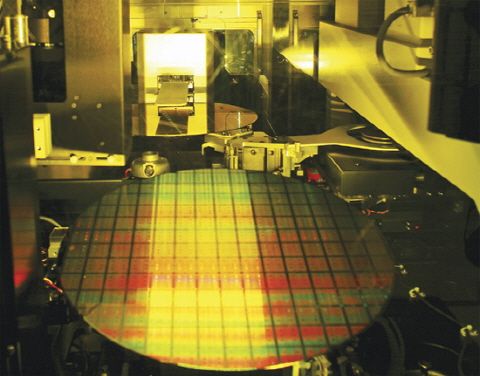

TSMC의 차세대 3D 패키징 기술인 CoWoS(chip-on-wafer-on-substrate)의 양산수율과 생산단가가 기대에 부합하지 못했기 때문이라는 분석이다.

4일 타이완 디지타임스는 이코노믹데일리뉴스를 인용해 알테라와 자일링스가 차세대 반도체 생산에 TSMC가 개발한 CoWoS 방식 대신 PoP(Package on Package) 기술을 적용하기로 했다고 보도했다.

관련기사

- 벌써?...TSMC, 애플 A6X 1분기중 시생산2013.03.05

- TSMC 애플 위해 100억달러 투입2013.03.05

- 인텔, 아톰·FPGA 결합된 첫 번째 제품군 선보여2013.03.05

- 자일링스, FPGA용량 100% 확대 신기술 발표2013.03.05

소식통에 따르면 자일링스와 알테라가 몇 년 내로 ASE와 SPIL로 생산 물량을 이동할 가능성이 있다고 지적했다. ASE와 SPIL은 모두 올해 PoP 기술을 적용한 생산라인 가동 계획을 밝힌 바 있다. 또 다른 파운드리 업체인 암코 역시 대안으로 거론된다.보도는 TSMC의 CoWoS 기술이 양산수율과 생산단가를 충족시키지 못한 것을 이 같은 변화의 원인으로 꼽았다. TSMC는 2015년까지 CoWoS 관련 사업부문에서 10억달러 매출을 기록하겠다는 목표를 세워두고 있다.

현재 시장 주류인 PoP 방식은 두 개 이상의 패키지를 수직으로 쌓아올리는 방식이다. TSMC가 최초로 적용한 CoWoS는 칩과 기판 중간에 실리콘인터포저를 삽입하고 TSV(실리콘관통전극) 기술을 적용한 3D 패키징 기술이다.