ARM 홀딩스가 코어텍스 제품군을 이용해 고성능 서버를 만들 수 있는 메모리 캐시 네트워크 디자인을 공개했다. 저전력 고밀도 서버 시장의 개화를 앞두고, ARM 서버에 대한 업계의 주목도를 더 북돋으려는 의도로 보인다. 새로운 서버 전쟁의 서막을 열었다는 평가다.

10일(현지시간) 외신에 따르면, ARM 홀딩스는 미국 새너제이에서 열린 한 컨퍼런스에서 코어텍스 프로세서 디자인에 기반한 서버 제작방법을 제시했다.

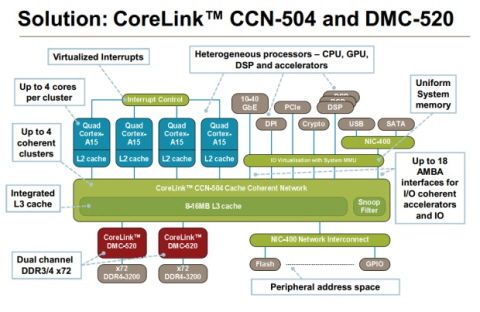

코어링크로 이름 붙여진 ARM홀딩스의 제안은 캐시 코히어런트 네트워크(CCN-504)란 8~16MB 용량의 공유 L3캐시를 핵심으로 한다. ARMv7 아키텍처 기반의 쿼드코어 코어텍스A15 4개와 각종 시스템온칩(SoC) 제품이 CCN-504란 영역을 중심에 두고 연결된다.

CCN-504란 기술 디자인은 SoC가 각 프로세서 코어와 연결될 때 캐시 역할을 하면서 메인메모리 컨트롤러, 주변장치(퍼리퍼럴) 컨트롤러 등까지 연결하는 중앙의 통로를 담당한다. 여기에 GPU나 코프로세서등을 추가해 성능을 더 높일 수 있다.

ARM 측은 이 기술이 병렬 컴퓨팅 워크로드를 지원하기 위한 목적이라고 밝혔다. 서버용이란 얘기다. 네일 파리스 ARM홀딩스 인터커넥트제품 매니저는 “이 디자인은 엔터프라이즈 서버에서 사용되는 병렬 워크로드와 멀티코어 운영체제에 더 최적화됐다”라며 “프로세서를 16코어까지 확장할 수 있으며, ARM을 위한 새 영역을 연 것”이라고 말했다.

향후 프로세서 코어수는 더 증가할 수 있다. 파리스 매니저는 “기본적인 인터커넥트 마이크로아키텍처를 디자인해 특정한 핫스팟과 병목현상이 없다”라며 “다른 CPU 클러스터 사이에서 훨씬 더 많은 병렬프로세싱을 예상가능하다”라고 강조했다.

이 디자인은 CPU에서 GPU로 데이터를 이동시키기 위해 L3 캐시를 공유하게 된다. 캐시 컨트롤러 네트워크는 1Tbps의 대역폭을 갖게 된다. 공유 L3캐시 네트워크 구조로 CPU와 GPU가 데이터를 주고 받을 필요가 거의 사라지는 형태다. ARM 측은 이로써 “데이터 처리 시간, 전력 등을 절감할 수 있다”고 설명했다.

이 캐시 코히어런트 네트워크 기술은 향후 출시될 64비트 ARMv8 프로세서 디자인과도 호환된다. ARMv8은 내년 출시되는 프로세서 디자인이다. ARM 측은 또한 향후 DSP와 다른 종류의 가속기를 SoC 형태로 구현할 계획을 갖고 있다고 덧붙였다.

코어링크 디자인 중 캐시 분야 외에 ARM홀딩스는 새 메모리 컨트롤러 기술도 선보였다. 서버 메모리는 DMC-520으로 불리는 컨트롤러로 CCN-504 캐시 코히어런트 네트워크에 연결된다. DMC-520은 DDR3 DRAM뿐 아니라 DDR4 메모리를 지원한다. 이는 애러보정코드(ECC)를 지원한다.

ARM의 서버 제작을 위한 캐시 네트워크 디자인 발표는 의미심장하다. 최근 IT업계는 데이터센터 에너지효율성 확보를 위해 ARM 아키텍처에 기반한 저전력 서버에 주목하고 있다. 시장조사업체와 HP 등은 ARM 등의 저전력 서버 시장이 향후 전체 시장의 10%를 차지할 것으로 전망한다.

관련기사

- 64비트 ARM 서버 시제품 연말 첫선2012.10.11

- 오픈스택, ARM 서버 테스트환경 무료 제공2012.10.11

- ARM 아키텍처 기반 서버, 연말에2012.10.11

- ARM, 64비트칩 공개…서버 시장 요동2012.10.11

ARM 프로세서는 저전력, 저발열 설계를 바탕으로 스마트폰이나 아이패드 같은 모바일 기기에 주로 사용된다. 그동안 멀티코어와 64비트 미지원 등 성능의 한계로 서버로 사용하기에 부족했던 ARM 프로세서는 최근 약점을 보완하면서 서버영역을 넘보고 있다. 현재 HP가 문샷 프로젝트를 통해 ARM 아키텍처 기반의 서버를 개발하고 있다.

ARM은 지속적으로 서버 영역 진출을 위한 무기를 만들어 내면서 시장 조기 안착을 위한 포석을 깔아나갈 것으로 예상된다.