인공지능(AI) 성능을 좌우하는 메모리 반도체 정확도를 100배, 처리 속도는 7.6배 정도를 개선할 수 있는 기술이 개발됐다.

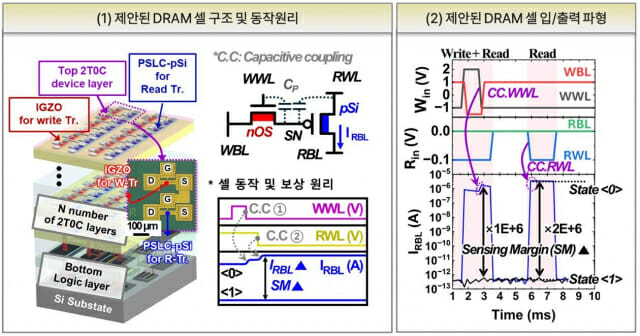

고려대학교는 유현용 전기전자공학부 교수와 DGIST 권혁준 교수 연구팀이 p-채널 실리콘과 n형 산화물 반도체를 집적한 ‘상보형 게인 셀(CGC) 구조’를 구현하는데 성공했다고 30일 밝혔다.

'p-채널 실리콘'은 실리콘 결정립 크기를 정밀 제어하는 방법으로 정보 처리 속도를 빠르게 하고, 안정성을 구현한 반도체 재료다. 또 n형 산화물 반도체는 전자를 제어해 전력 손실을 최소화하고 데이터 유지력을 극대화하는 소재로 쓰인다.

연구팀은 "3차원 반도체 적층에서는 저온 공정이 필수다. 그러다보니 n형 산화물 반도체가 소자간 불필요한 간섭 현상을 일으켜 데이터를 정확히 읽어내는 '센싱마진'이 급격히 저하되는 고질적인 문제가 있었다"고 설명했다.

연구팀은 이에 n형 산화물 반도체와 p-채널 실리콘을 결합한 'CGC' 구조를 개발했다. n형 산화물 반도체는 전력 소모를 줄이면서 데이터를 오래 보관할 수 있고, p-채널 실리콘은 정보를 빠르고 정확하게 읽어낼 수 있다. 이 두 장점을 결합했다.

연구팀에 따르면 이번에 개발한 CGC 구조는 기존에 방해가 됐던 용량성 결합 현상을 오히려 전압을 증폭시키는 유리한 기제로 전환, 센싱 마진을 기존 방식 10⁴보다 100배 이상 높은 10의 6승 수준까지 끌어올렸다. 이는 1,024개 셀이 연결된 대규모 환경에서도 안정적인 동작이 가능한 수치다.

이와함께 저온 공정을 통해 레이저 결정화 실리콘 소자 중 세계 최대 크기인 32.3µm 결정립도 확보했다. 결정립이 클수록 정공 이동도(동작 속도)가 빨라진다.

연구팀은 "CGC 구조는 기존 산화물 기반 소자보다 월등히 빠른 265cm²/Vs의 동작 속도를 기록했다. 시뮬레이션 결과, 읽기 시간은 11.8ns로 기존 n형 산화물 반도체 전용 셀(90.1ns) 대비 약 7.6배 빨라졌다. 유지시간도 1,000조 이상 달성했다"고 말했다.

관련기사

- SK하이닉스 "AI 시대 협력사와 공급망 경쟁력 강화"2026.04.20

- GPU·HBM 필요없는 인공지능 반도체 나왔다2026.03.05

- "캐패시터 없는 DRAM으로 데이터 1천초 유지"2026.04.14

- "메모리 부족 여파…내년 16GB 램 스마트폰 사라진다"2025.12.15

유현용 교수는 “이번에 개발된 레이저 기반 공정 기술은 3D 적층 반도체 기술 상용화를 앞당기는 핵심 동력이 될 것”이라며 “향후 차세대 지능형 반도체, 고성능 인공지능 칩, 고용량 메모리, 초고속 통신 칩 등 고집적·고성능 반도체 개발에 필수적인 기반 기술로 활용될 것"으로 전망했다.

연구결과는 반도체 소자 분야 국제 학회(2026 IEEE/JSAP symposium on VLSI technology & circuits)에서 오는 6월 발표한다.