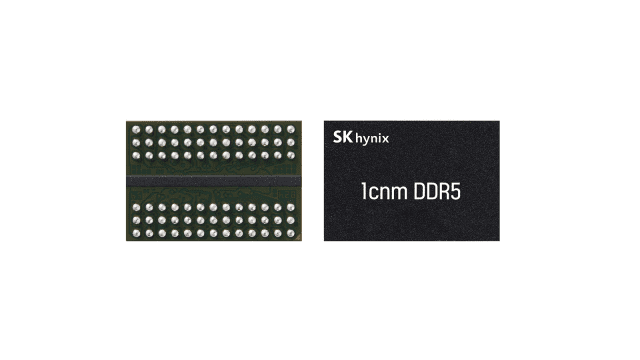

SK하이닉스가 차세대 D램 개발서 EUV(극자외선) 공정을 적극 활용하고 있다. 올 하반기 전환투자가 시작되는 1c(6세대 10나노급) D램의 경우, EUV 적용 층 수를 이전 세대 대비 2개 늘어난 5개 이상까지 적용하기로 했다. 차세대 EUV 기술을 위한 소재 개발도 지속하고 있다.

11일 업계에 따르면 SK하이닉스는 1c D램에 EUV 레이어 수를 총 5개 이상 적용할 계획이다.

EUV는 기존 반도체 노광공정 소재인 ArF(불화아르곤) 대비 빛의 파장이 13분의 1 수준으로 짧아(13.5나노미터), 초미세 공정 구현에 용이한 광원이다. 다만 기술적 난이도 및 설비 도입 비용이 높아, 초미세 회로 구현이 필요한 특정 층(레이어)에만 적용되고 있다. 나머지 층에는 DUV(심자외선) 등 기존 레거시(성숙) 공정이 쓰인다.

SK하이닉스의 경우, 1a(4세대 10나노급) D램의 1개 레이어에 EUV를 처음 적용한 바 있다. 이후 1b D램에서는 이를 4개까지 확대했다.

나아가 1c D램에서는 EUV 레이어 수를 5개 이상 늘린다. 1c D램은 아직 본격적인 상용화 궤도에 오르지 않은 차세대 D램으로, SK하이닉스는 지난해 세계 최초로 1c 공정 기반의 16Gb(기가비트) DDR5 D램을 개발한 바 있다. 올 하반기부터는 1c D램의 전환투자를 시작할 예정이다.

박의상 SK하이닉스 TL은 이날 수원컨벤션센터에서 열린 '차세대 리소그래피+패터닝 학술대회'에서 "1c D램에 EUV 레이어를 5개 이상 적용하고, 1d·0a 등 차세대 제품에도 EUV를 모두 사용할 것"이라며 "이에 맞춰 SK하이닉스는 EUV 공정의 생산성을 증가시킬 수 있는 방안에 초점을 두고 많은 개발을 진행하고 있다"고 설명했다.

향후 도입될 High-NA(고개구수) EUV 기술에 대해서도 적극 대응하고 있다. NA는 렌즈 수차로, 해당 수치를 높일 수록 해상력이 향상된다. 기존 EUV의 렌즈 수차는 0.33 수준이나, High-NA EUV는 0.55로 더 높다. SK하이닉스는 이르면 내년 High-NA EUV 설비를 도입할 계획이다.

특히 High-NA EUV용 마스크 개발이 주요 난제가 될 것으로 관측된다. 마스크는 웨이퍼에 반도체 회로를 새기기 위해 사용되는 소재다.

EUV는 거의 모든 물질에 흡수되는 성질을 지녀, 거울을 통해 웨이퍼에 빛을 반사시키는 방식을 활용한다. 그런데 High-NA에서는 빛이 더 넓은 각도로 퍼져, 입사각과 반사각이 겹치는 문제가 발생하게 된다.

이에 업계는 빛의 세로 방향을 가로 대비 2배 더 축소시켜 빛이 겹치지 않게 하는 '아나모픽' 기술을 고안해냈다. 마스크에서 웨이퍼로 투사되는 빛이 기존에는 가로 세로 모두 4배 축소됐다면, 아나모픽에서는 가로는 4배 그대로, 세로는 8배로 축소하는 방식이다. 웨이퍼에 투사되는 면적이 줄어드는 만큼, 마스크는 2개를 사용해야 한다.

관련기사

- SK하이닉스 미래 성장성, HBM4 가격협상·수익 방어에 달렸다2025.07.24

- SK하이닉스 "올해 신규 투자 HBM에 집중...내년 고객물량 가시성 확보"2025.07.24

- SK하이닉스, 올 하반기 차세대 '1c D램' 전환투자 개시2025.07.24

- "HBM3E 12단 본격 확대"…SK하이닉스, 2분기 역대 최대 매출·영업익 달성2025.07.24

다만 마스크를 2개 사용하는 과정에서, 마스크끼리 맞닿은 부분이 겹치는 문제가 발생하게 된다. SK하이닉스는 이를 '스티칭(Stiching)' 영역이라고 부른다.

박 TL은 "스티칭 영역에 대한 제어가 상당히 어렵기 때문에, 당사도 현재 High-NA EUV용 마스크는 개발을 못한 상황"이라며 "어떠한 물질로 만들어야할 지 계속 시도는 하고 있는 상태"라고 말했다.