삼성전자가 지난해 하반기부터 최첨단 D램의 재설계를 칩 사이즈를 키우는 방향으로 진행 중인 것으로 파악됐다. 생산성과 성능 보다는 '수율(투입품 대비 양품 비율)'에 무게를 둔 전략으로, HBM(고대역폭메모리) 등 고부가 메모리의 안정적인 양산에 역량을 집중하려는 전략으로 풀이된다.

10일 업계에 따르면 삼성전자는 지난해 하반기부터 1c(6세대 10나노급) D램의 칩 사이즈를 기존 대비 키워 개발을 진행하고 있다.

1c D램은 삼성전자가 올해 하반기 양산을 목표로 한 차세대 D램이다. 회로 선폭은 11~12나노미터(nm) 수준이다. 이전 세대인 1b(5세대) D램은 12~13나노 대로 추산된다.

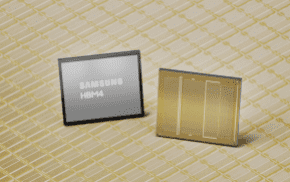

삼성전자는 1c D램을 차세대 HBM4(6세대 HBM)에 우선적으로 적용할 계획이다. 주요 경쟁사 대비 한 세대 앞선 D램으로 HBM의 경쟁력을 빠르게 끌어올리겠다는 의도가 깔려 있다. SK하이닉스·마이크론 등은 HBM4에 1b D램을 채택하기로 했다.

다만 삼성전자의 1c D램은 개발 초기부터 수율 개선에 난항을 겪어 왔다. 지난해 하반기 첫 양품을 확보했으나, 수율을 만족스러운 수준까지 구현하지는 못한 것으로 알려졌다.

주요 배경은 생산성이다. 당초 삼성전자는 경쟁사를 의식해 1c D램의 칩 사이즈를 당초 계획 대비 줄이기로 했다. 칩 사이즈가 작아질수록 웨이퍼 투입량 대비 생산량이 많아져, 제조 비용 효율화에 유리하다. 다만 이로 인해 안정성이 떨어진다는 지적이 제기돼 왔다.

이에 삼성전자는 지난해 말 1c D램의 설계를 일부 수정하기로 했다. 핵심 회로의 선폭은 최소한으로 유지하되, 주변 회로의 선폭 기준을 완화해 수율을 빠르게 끌어올리는 것이 주 골자다.

사안에 정통한 복수의 관계자는 "삼성전자가 1c D램의 칩 사이즈를 키우는 쪽으로 설계를 변경한 뒤, 올해 중순을 목표로 수율 향상에 열을 올리고 있다"며 "비용이 더 들더라도 차세대 메모리의 안정적 양산에 초점을 맞춘 것으로 보인다"고 설명했다.

관련기사

- 삼성전자, '1c D램' 양산 투자 개시…차세대 HBM4 본격화2024.12.09

- 삼성전자, 갤럭시S25향 모바일 '1b D램' 공급 난항2024.09.04

- 삼성전자, 차세대 D램 전환투자 전략 고심…연내 윤곽 나올 듯2024.09.12

- 삼성전자, CXL 2.0 D램 하반기 양산 시작…"1y D램 탑재"2024.07.18

설계가 변경된 1c D램의 유의미한 수율을 논하기에는 아직 이르다는 평가다. 삼성전자 안팎에서는 오는 5~6월께 구체적인 결과가 도출될 것으로 기대하고 있다.

한편, 비슷한 이유에서 1b D램의 일부 제품도 수율 향상을 위한 재설계가 이뤄지고 있다. 현재 서버용 32Gb(기가비트) 1b D램 제품의 수율을 양산 수준인 70~80%대까지 끌어올리는 작업이 진행 중인 것으로 알려졌다.