최첨단 패키징 기술인 W2W 하이브리드 본딩이 미래 반도체 시장의 핵심 요소로 떠오를 전망이다. 특히 2나노미터(nm) 이하에서 상용화될 BSPDN, CFET 등이 유력한 적용처로 떠오르고 있다.

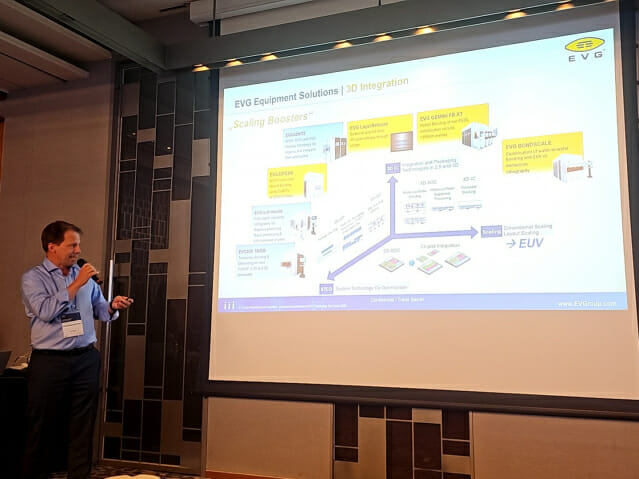

한국EV그룹(EVG)는 13일 코트야드 메리어트 서울 판교에서 'EVG 테크놀로지 데이'를 열고 최첨단 본딩 기술의 시장 전망에 대해 밝혔다.

오스트리아에 본사를 둔 EVG는 반도체 및 디스플레이 후공정용 장비를 전문으로 개발하는 업체다. 웨이퍼 본딩장비 및 나노임프린트(NIL), 얼라이너, 코터, 적외선(IR) 계측 시스템 등을 개발해 왔다.

특히 EVG는 W2W 등 첨단 하이브리드 본딩 시장에 주력하고 있다.

하이브리드 본딩은 두 반도체 칩을 구리 배선은 구리 배선끼리, 절연 물질은 절연 물질끼리 각각 접합하는 기술이다. 기존 칩 연결에 쓰이던 솔더볼·범프 등을 쓰지 않아 패키지 두께를 줄이고, 전기적 특성 및 방열 특성을 높일 수 있다.

하이브리드 본딩은 패키징을 웨이퍼, 혹은 개별 다이(Die)에서 수행하는지에 따라 W2W(웨이퍼-투-웨이퍼), D2D(다이-투-다이), D2W(다이-투-웨이퍼) 등으로 나뉜다. 이 중 W2W는 웨이퍼끼리의 연결로 생산성이 높다는 장점이 있다.

EVG가 전망하는 W2W 하이브리드의 유망한 적용처는 BSPDN(Back Side Power Delivery Network), CFET(Complementary FET) 등 첨단 반도체 공정이다.

BSPDN은 웨이퍼 전면에 모두 배치되던 신호처리와 전력 영역을 분리해, 웨이퍼 후면에 전력 영역을 배치하는 기술이다. 삼성전자가 내년 양산 예정인 2나노 공정에 BSPDN을 첫 적용하기로 하는 등 주요 반도체 기업들로부터 많은 주목을 받고 있다.

CFET은 가장 최근 상용화된 트랜지스터 구조인 GAA(게이트-올-어라운드)를 또 한번 뛰어넘는 기술이다. 향후 1나노급 공정에서 적용될 것으로 점쳐진다.

관련기사

- HBM4 두께 표준 '완화' 합의…삼성·SK, 하이브리드 본딩 도입 미루나2024.03.08

- AMAT, 첨단 패키징용 하이브리드본딩·TSV 기술 선봬2023.07.18

- EVG, 3D 적층 기술 혁신하는 '나노클리브' 신기술 발표2024.01.30

- 삼성전자, 2027년 2나노 신공정 추가..."AI 시대 원스톱 솔루션 제공"2024.06.13

기존 트랜지스터 내부에는 +극을 인가하면 전류를 발생시키는 p형 반도체(pMOS)와 -극을 인가하면 전류를 발생시키는 n형 반도체(nMOS)가 수평적으로 집적돼 있다. 반면 CFET은 이 nMOS와 pMOS를 수직으로 적층한다. GAA 트랜지스터가 위로 겹겹이 적층되는 셈이다.

토스튼 마티아스 EVG 아시아태평양 세일즈 총괄은 "BSPDN 혹은 새로운 트랜지스터 구조를 구현하려면 첨단 웨이퍼 본딩 공정이 단일, 혹은 복수로 적용돼야 한다"며 "EVG는 이러한 솔루션을 위한 본딩 장비를 적용처별로 보유하고 있다"고 설명했다.