삼성전자가 차세대 D램으로 주목받는 VCT(수직 채널 트랜지스터) D램과 3D D램 개발에 열을 올리고 있다. VCT D램은 내년 초기 제품 개발을 완료할 예정이며, 3D D램은 셀을 16단까지 적층하는 방안을 추진 중인 것으로 알려졌다.

이시우 삼성전자 부사장은 지난 14일 서울 광진구 그랜드 워커힐 호텔에서 열린 '국제 메모리 워크숍(IMW) 2024' 행사에서 회사의 차세대 D램 기술력에 대해 발표했다.

이날 '메모리 산업을 위한 첨단 채널 물질' 토론에 참석한 이 부사장은 "하이퍼스케일러 AI와 온디멘드 AI 등 산업 발전은 많은 메모리 처리능력을 요구한다"며 "반면 기존 D램의 미세 공정 기술이 한계에 다다르면서, 셀(데이터가 저장되는 단위) 구조에 새로운 혁신이 일어날 것으로 예상된다"고 밝혔다.

새로운 셀 구조의 D램은 크게 '4F스퀘어(4F²) VCT D램'과 '3D D램'으로 구분할 수 있다.

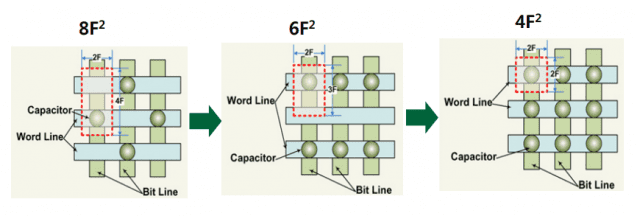

D램의 셀은 하나의 트랜지스터와 하나의 커패시터로 구성된다. 트랜지스터는 전기 스위칭과 전압 증폭을 위한 소자다. 전류가 흐르는 방향에 따라 소스·게이트·드레인 순으로 구성된다. 드레인 위에 위치한 커패시터는 전하를 일시적으로 저장하는 소자를 뜻한다.

이 셀을 동작시키기 위해서는 게이트 단자로 전압이 인가되는 워드라인(WL)과, 드레인 단자로 인가되는 비트라인(BL)이 바둑판 형식으로 배열된다.

초창기 D램의 셀 구조는 비트라인 4칸, 워드라인 2칸으로 구성된 8F스퀘어였다. 그러다 80나노급 D램부터는 6F스퀘어(비트라인 3칸, 워드라인 2칸)가 적용됐다. 셀 면적이 줄어들수록 D램의 집적도 및 성능을 끌어올릴 수 있다.

4F스퀘어로 나아가기 위해서는 셀 구조가 크게 변화해야 한다. 기존 D램은 트랜지스터를 수평으로 배치했으나, 4F스퀘어 구현을 위해서는 이를 수직으로 배치하는 VCT구조가 필요하다.

이 부사장은 "많은 기업들이 4F스퀘어 VCT D램으로의 전환을 위해 노력하고 있다"며 "다만 이를 위해서는 산화물 채널 물질, 강유전체 등 새로운 소재 개발이 선행돼야 한다"고 설명했다.

이와 관련해, 삼성전자는 내년 4F스퀘어 VCT D램에 대한 초기 샘플을 개발할 예정인 것으로 알려졌다.

관련기사

- 삼성전자 "2Q 서버용 D램 50%, 낸드 100% 이상 출하량 확대"2024.04.30

- 삼성전자 작년 4분기 D램 점유율 45.5% 1위...매출 반등2024.03.06

- 삼성전자, 작년 4분기 D램 점유율 1위 45.7%...7년만에 최고치2024.02.27

- 삼성전자, 3D D램 상용화 임박...송재혁 사장 "최선 다하는 중"2024.01.31

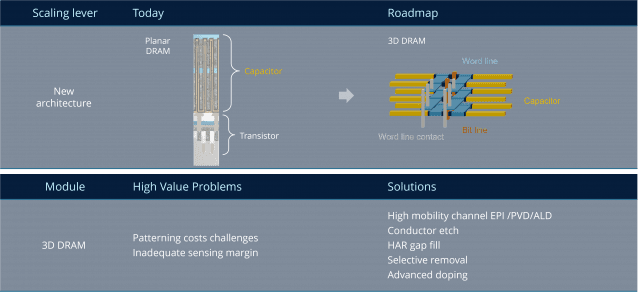

나아가 삼성전자는 2030년 상용화를 목표로 3D D램도 개발 중이다. 3D D램은 비트라인, 혹은 워드라인을 수직으로 세워 셀을 수직으로 적층하는 기술이다. 해당 D램에도 새로운 소재는 물론, 웨이퍼와 웨이퍼를 직접 붙이는 웨이퍼본딩(W2W) 기술이 도입돼야 한다.

현재 3D D램을 개발하는 주요 메모리 기업들은 셀을 16단까지 적층해 상용화 가능성을 검토 중인 것으로 전해진다. 미국 마이크론의 경우 8단 적층을 시도 중인 것으로 관측된다.