"차세대 패키징 시장에서는 융복합 기술이 핵심 요소가 될 것이라고 생각한다. 메모리와 로직, 컨트롤러 등이 하나의 패키지로 연결되는 2.5D, 3D 패키징 등이 대표적이다. SK하이닉스도 HBM을 보다 잘 만들기 위해 내부적으로 공부를 하고 있다."

문기일 SK하이닉스 부사장은 26일 서울 코엑스에서 열린 '첨단 전자실장 기술 및 시장 세미나'에서 SK하이닉스의 HBM용 패키징 기술 동향에 대해 이같이 밝혔다.

이날 문 부사장은 "2010년대까지 패키징 기술은 얼마나 칩을 많이 쌓아 메모리 밀도를 높일 수 있는지(스태킹)에만 주력했다"며 "이제는 어떠한 패키징을 적용하느냐에 따라 칩의 특성이 바뀔 수 있다는 퍼포먼스 관점으로 나아가고 있다"고 설명했다.

그는 이어 "차세대 패키징 기술은 2.5D와 같이 메모리와 로직·컨트롤러 등이 융복합되는 방향으로 나아가고 있어 우리나라도 차근차근 기술을 확보해나가야 한다"며 "SK하이닉스도 HBM을 더 강건하게 만들기 위해 이러한 기술을 내부적으로 공부하고 있다"고 덧붙였다.

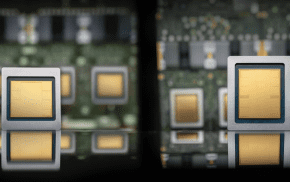

2.5D 패키징은 넓은 기판 모양의 실리콘 인터포저 위에 반도체 다이(Die)를 수평 배치하는 기술이다. 기판만을 활용하는 기존 2D 패키징에 비해 회로를 더 밀도있게 연결할 수 있다. 대표적으로 대만 주요 파운드리 TSMC는 자사의 2.5D 패키징에 'CoWoS'라는 브랜드를 붙이고, AI반도체와 HBM을 하나의 칩에 집적하는 공정을 수행하고 있다.

HBM은 여러 개의 D램을 수직으로 적층해, 데이터 처리 성능을 기존 D램 대비 크게 끌어올린 차세대 메모리다.

각 D램을 연결하기 위해서는 칩에 미세한 구멍을 뚫은 뒤, 수천 개의 TSV(실리콘관통전극)를 통해 상하단의 구멍을 연결하는 공정이 활용된다. TSV는 기존 칩을 연결하는 와이어 본딩 대비 데이터 처리 속도와 소비전력을 향상시키는 데 유리하다.

문 부사장은 "HBM은 매우 고속으로 작동하기 때문에 서멀(열)을 얼마나 잘 배출하는 지가 패키징에서 가장 중요한 요소가 될 것"이라며 "이에 SK하이닉스는 HBM2E부터 MR-MUF 공법을 적용하고 있다"고 설명했다.

MR-MUF는 HBM 전체에 열을 가해 납땜을 진행하고, 칩 사이에 액체 형태의 보호재를 넣어 공백을 채우는 공정이다. 또 다른 본딩 기술인 NCF 대비 열이 골고루 가해져 신뢰성이 높고, 생산 효율성이 높다는 평가를 받고 있다.

관련기사

- SK하이닉스, TSMC 테크 행사서 'HBM·패키징 협력 관계' 강조2024.04.25

- AI메모리 날개 단 SK하이닉스, 1Q 깜짝실적..."HBM 투자 늘린다"2024.04.25

- SK하이닉스 "연말 일반 D램 캐파, 22년 피크 수준에 미치지 못할 것"2024.04.25

- SK하이닉스, "16단 HBM4도 MR-MUF 유지할 것"2024.04.25

다만 MR-MUF는 웨이퍼의 끝단이 휘는 워피지 현상에 취약하다는 단점이 있다. 특정 영역에서 보호재가 골고루 발리지 않는 보이드 현상도 MR-MUF의 신뢰성에 악영향을 미치고 있다.

문 부사장은 "다행히 HBM 개발 초창기보다 워피지 현상을 줄이는 데 성공했고, 현재도 이를 극복하기 위한 기술을 개발 중"이라며 "보이드를 줄이는 것도 SK하이닉스의 기술적인 당면 과제"라고 설명했다.