SK하이닉스가 차세대 HBM(고대역폭메모리)에도 첨단 패키징 기술인 MR-MUF(매스 리플로우-몰디드 언더필)를 고수할 예정이다. 대안격으로 떠올랐던 하이브리드 본딩 기술은 HBM의 표준 완화에 따라 도입 속도가 늦춰질 것으로 내다봤다.

SK하이닉스는 25일 2024년 1분기 실적발표 컨퍼런스콜에서 "차세대 HBM 패키징의 높이 기준이 완화되면 하이브리드 본딩 적용 시점이 다소 늦어질 것으로 예상된다"고 밝혔다.

회사는 이어 "하이브리드 본딩 초기 도입 시점에는 생산성과 품질 리스크가 존재할 가능성이 있다"며 "기술 성숙도를 높인 뒤 적용하는 것이 원가 및 경쟁력 측면에서 유리할 것"이라고 덧붙였다.

HBM은 여러 개의 D램을 수직으로 적층한 뒤, TSV(실리콘관통전극)을 통해 연결한 차세대 메모리다. HBM3E(5세대 HBM)까지 상용화가 완료됐다. 적층된 D램 개수는 현재 8단이 최대이며, 12단 HBM3E에 대한 고객사 검증이 진행되고 있다.

오는 2026년 상용화 예정인 HBM4(6세대 HBM)는 12단, 16단 적층 제품으로 개발이 진행 중이다.

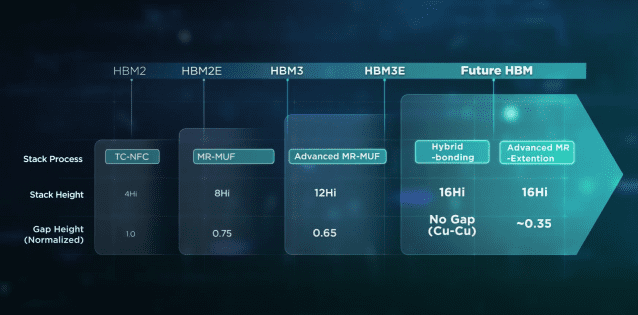

그간 업계가 주목해 온 HBM4의 최대 화두는 '패키징' 기술이다. 삼성전자·SK하이닉스는 적층된 각 D램을 작은 돌기 형태의 마이크로 범프를 통해 전기적으로 연결하는 TC(열압착) 본딩 기술을 HBM3E 제품까지 적용해 왔다.

기업별로 세부적인 본딩 방식은 다르지만(삼성전자: NCF, SK하이닉스: MR-MUF), 범프를 사용한다는 점은 동일하다.

그러나 HBM4에서는 TC 본딩의 유지가 불가능할 것이라는 의견이 제기된 바 있다. 12단 적층까지는 국제반도체표준화기구(제덱, JEDEC)가 정한 HBM의 높이 표준인 720마이크로미터(μm)로 구현할 수 있으나, 16단 적층은 패키징이 너무 두꺼워져 표준을 충족하기가 매우 어렵다.

때문에 메모리 기업들은 기존 TC 본딩과 더불어 하이브리드 본딩 기술을 병행 개발해 왔다. 하이브리드 본딩은 칩과 웨이퍼의 구리 배선을 직접 붙이는 기술로, 범프를 쓰지 않아 패키지 두께를 줄이는 데 훨씬 용이하다.

다만 하이브리드 본딩은 관련 소재·장비 기술력이 안정화되지 않아 아직 상용화 단계에 이르지 못하고 있다. 또한 하이브리드 본딩 도입 시 막대한 설비투자를 진행해야 하고, 초기 수율 안정화에도 상당한 비용이 든다는 문제점이 있다.

이러한 기업들의 고민은 최근 제덱 회원사들이 HBM4의 패키징 두께를 기존보다 높은 775마이크로미터로 합의하면서 상당 부분 해소됐다. 775마이크로미터가 표준으로 제정되면, 기존 TC 본딩으로도 16단 제품을 충분히 구현할 수 있다는 게 업계의 지배적인 시각이다.

관련기사

- SK하이닉스 "추가 클린룸 필요해...올해 투자 규모, 연초 계획보다 증가"2024.04.25

- SK하이닉스 "12단 HBM3E 내년 공급...고객사와 장기 프로젝트 논의중"2024.04.25

- SK하이닉스, 1분기 영업익 2.8조 '어닝 서프라이즈'..."AI 메모리 덕분"2024.04.25

- [1보] SK하이닉스, 1분기 영업익 2.8조…흑자전환2024.04.25

SK하이닉스 역시 이날 컨퍼런스콜에서 "경쟁력이 입증된 어드밴스드 MR-MUF 공정을 16단 HBM에도 적용할 예정"이라며 "생산 효율성이 높고 경쟁력 있는 제품 공급을 지속해 나갈 수 있을 것"이라고 강조했다.

MR-MUF는 HBM 전체에 열을 가해 납땜을 진행하고, 칩 사이에 액체 형태의 보호재를 넣어 공백을 채우는 공정이다. MR-MUF는 칩이 휘어지는 워피지 현상이 발생할 수 있으나, SK하이닉스는 이를 칩 제어 기술과 신규 보호재 적용으로 신뢰성을 높인 어드밴스드 MR-MUF 기술로 대응하고 있다.