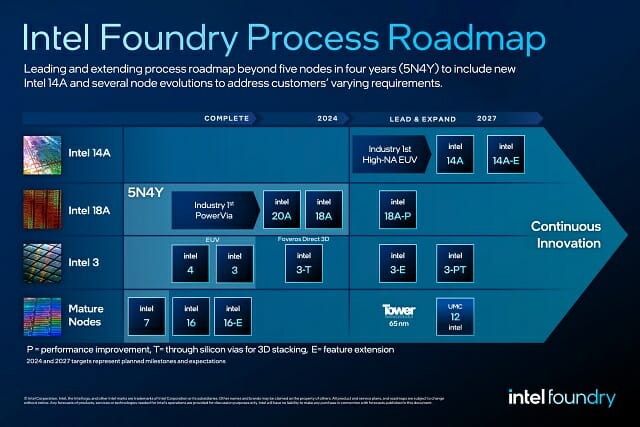

인텔이 지금까지 개발한 DUV(심자외선)/EUV(극자외선) 기반 반도체 생산 공정을 지속 보완해 향후 출시할 자사 제품이나 IFS(인텔 파운드리 서비스) 외부 고객사에 적용한다고 밝혔다.

인텔은 21일(미국 현지시간, 한국시간 22일 1시) 미국 캘리포니아주 새너제이에서 진행된 파운드리 생태계 행사 'IFS 다이렉트 커넥트 2024' 기조연설을 통해 향후 3년간 반도체 공정 로드맵을 공개했다.

인텔은 이 행사에서 최선단 반도체 생산 공정 '인텔 14A'를 오는 2027년부터 적용함과 동시에 기존 공정도 지속 보완할 예정이라고 밝혔다. 각 공정 명칭 뒤에는 E, T, P 등 알파벳을 붙여 구분을 돕는다.

공정 뒤의 'E'는 '기능 확장'을, 'T'는 전기 배선과 신호 등이 지나갈 수 있는 TSV(실리콘 관통전극)를 추가해 반도체 다이(Die)를 수직으로 쌓을 수 있는 적층 구조를, 'P'는 소모 전력 감소 등 성능 개선을 의미한다.

이날 인텔이 공개한 로드맵에 따르면, 인텔은 EUV 기반 '인텔 3' 공정에 이어 수직 적층 가능 구조를 적용한 '인텔 3-T'를 올해 안에 개발할 예정이다.

이어 2027년까지 고전압 환경 대응 기능 등을 추가한 '인텔 3-E', 성능을 대폭 개선하고 TSV를 추가한 '인텔 3-PT' 등을 투입한다.

내년 상반기부터 양산에 들어가는 1.8나노급 '인텔 18A' 공정에 이어 성능을 향상한 '인텔 18A-P' 개발도 예정돼 있다.

인텔이 고개구율(High-NA) EUV 기술을 이용해 2027년부터 투입할 1.4나노급 최선단 미세공정 '인텔 14A' 이외에 일부 기능을 확장한 '인텔 14A-E'도 선보인다.

관련기사

- 인텔, AI 시대 겨냥한 '인텔 파운드리' 본격 출범2024.02.22

- 인텔, 1.4나노급 초미세공정 '인텔 14A' 로드맵 공개2024.02.22

- 인텔, 학계·업계 인사로 파운드리 자문 위원회 구성2024.02.22

- 美 정부, 인텔에 10조원대 반도체 지원금 지급 논의2024.02.18

인텔은 기존 DUV 기반 공정 개발에도 지속적으로 투자하겠다고 밝혔다. 기존 인텔 22나노급 공정의 전력 소모를 낮춰 자동차 등 반도체나 통신 영역을 겨냥한 '인텔 16' 공정에는 이미 파생 공정인 '인텔 16-E'가 존재한다.

인텔이 가지고 있는 3차원 트랜지스터 구조 '핀펫'(FinFET)과 대만 파운드리 업체 UMC(聯華電子)의 설계 노하우를 결합한 12나노급 새 공정 '인텔 12' 역시 2027년부터 양산 예정이다.