오는 2026년 상용화를 앞둔 6세대 고대역폭메모리(HBM4)를 두고 업계의 고심이 깊어지고 있다. HBM4 제조의 핵심인 패키징 공정에 기존 본딩(접합) 기술을 이어갈지, 새로운 하이브리드 본딩 기술을 적용해야 할지 명확한 결론이 나지 않아서다.

메모리 업계는 비용 문제 상 기존 본딩 방식을 고수하자는 기류다. 그러나 그간 고객사가 요구해 온 HBM4의 두께 조건을 충족하기 위해서는, 패키징 축소에 유리한 하이브리드 본딩 도입이 필요하다는 의견이 다수였다.

하지만 메모리 업계가 기존 본딩 방식을 고수할 수 있는 가능성도 충분한 상황이다. 현재 HBM4의 규격을 정하는 표준화기구 '제덱(JEDEC)'에서 HBM4의 패키징 두께 요건을 완화하는 합의가 진행되고 있는 것으로 알려졌다.

21일 업계에 따르면 삼성전자, SK하이닉스를 비롯한 주요 반도체 기업들은 HBM4의 두께를 이전 세대와 비슷한 720㎛(마이크로미터), 혹은 이보다 두꺼운 775마이크로미터로 정하는 방안을 논의 중이다.

HBM은 여러 개의 D램을 수직으로 적층해 TSV(실리콘관통전극)으로 연결한 메모리다. 기존 D램 대비 데이터 처리 성능이 월등히 높아 AI 산업의 핵심 요소로 자리잡고 있다.

현재 HBM은 4세대인 HBM3까지 상용화에 이른 상태다. 올해에는 5세대인 HBM3E가, 오는 2026년에는 6세대인 HBM4가 본격 양산될 예정이다.

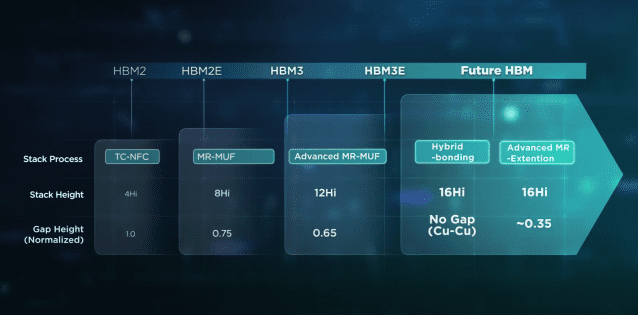

특히 HBM4는 정보를 주고받는 통로인 입출력단자(I/O)를 이전 세대 대비 2배 많은 2024개로 집적해, 메모리 업계에 또다른 변혁을 불리 일으킬 것으로 기대된다. 적층되는 D램 수도 최대 16개로 이전 세대(12개)보다 4개 많다.

■ HBM4 성능 뛰어나지만…패키징 한계 다다라

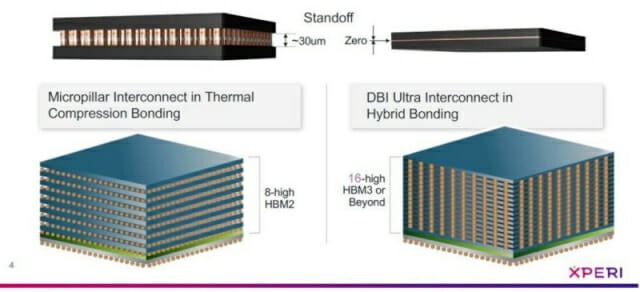

문제는 HBM 제조의 핵심인 패키징 기술의 변화다. 기존 HBM은 각 D램에 TSV 통로를 만들고, 작은 돌기 형태의 마이크로 범프를 통해 전기적으로 연결해주는 구조로 만들어진다.

세부적인 공법은 각 사마다 다르다. 삼성전자는 D램 사이사이에 NCF(비전도성 접착 필름)을 집어넣고 열압착을 가하는 TC 본딩을 활용한다. SK하이닉스는 HBM 전체에 열을 가해 납땜을 진행하고, 칩 사이에 액체 형태의 보호재를 넣어 공백을 채우는 MR-MUF(매스 리플로우-몰디드 언더필) 기술을 채택하고 있다.

다만 HBM4에서는 기존 마이크로 범프를 통한 본딩 적용이 어렵다는 평가가 지배적이었다. D램을 16단으로 더 많이 쌓으면서 발생하는 워피지(휨 현상), 발열 등의 요소들도 있지만, 기존 12단 적층과 같은 720마이크로미터 수준의 높이를 맞춰야 하는 것이 가장 큰 난관으로 꼽힌다.

D램을 더 많이 쌓으면서도 높이를 일정하게 유지하려면 각 D램 사이에 위치한 수십㎛ 크기의 마이크로 범프를 제거하는 것이 효과적이다. 각 D램의 표면을 갈아 얇게 만드는 기술(씨닝)도 방법 중 하나지만, 신뢰성을 담보하기가 어렵다.

때문에 업계는 하이브리드 본딩을 대안으로 주목해 왔다. 하이브리드 본딩은 칩과 웨이퍼의 구리 배선을 직접 붙이는 기술로, 범프를 쓰지 않아 패키지 두께를 줄이는 데 유리하다. 삼성전자, SK하이닉스 역시 이 같은 관점에서 공식행사 등을 통해 하이브리드 본딩 기술의 HBM4 적용 계획에 대해 언급한 바 있다.

■ HBM4 본딩 '투트랙' 전략의 배경…기술·비용적 난관

다만 삼성전자, SK하이닉스가 HBM4에 하이브리드 본딩 기술을 100% 적용하려는 것은 아니다. 양사 모두 기존 본딩, 하이브리드 본딩 기술을 동시에 고도화하는 투트랙 전략을 구사 중이다.

이유는 복합적이다. HBM4용 하이브리드 본딩 기술이 아직 고도화되지 않았다는 주장과, 기존 본딩 대비 생산단가가 지나치게 높다는 의견 등이 업계에서 제기되고 있다.

반도체 장비업계 관계자는 "하이브리드 본딩과 관련한 장비, 소재 단에서 일부 제반 기술이 아직 표준도 정해지지 않아 개발이 힘들다"며 "현재 국내 주요 메모리 업체들과 테스트를 진행하고 있으나, HBM4부터 해당 기술이 적용될 가능성이 명확하지 않은 이유"라고 설명했다.

일례로 하이브리드 본딩 공정은 진공 챔버 내에서 D램 칩에 플라즈마를 조사해, 접합부 표면을 활성화시키는 과정을 거친다. 기존 패키징 공정에서는 쓰이지 않던 기술로, 하이브리드 본딩의 난이도를 높이는 데 기인하고 있다.

시장 측면에서는 제조 비용의 증가가 가장 큰 걸림돌이다. 하이브리드 본딩을 양산화하려면 신규 패키징 설비투자를 대규모로 진행해야 하고, 초기 낮은 수율을 잡기 위한 보완투자가 지속돼야 한다.

실제로 국내 한 메모리 제조업체는 최근 진행한 비공개 NDR(기업설명회)에서 "기존 본딩과 하이브리드 방식 모두 개발 중이지만, 하이브리드 본딩은 단가가 너무 비싸다"고 토로하기도 했다.

결과적으로 메모리 제조업체들은 고객사의 요구 조건을 모두 충족한다는 전제 하에, HBM4에서의 하이브리드 본딩 도입을 가능하다면 피하고 싶어하는 입장이다.

한 반도체 업계 관계자는 "고객사가 요구하는 HBM4 높이의 제한(720마이크로미터)이 풀리면, 공급사로서는 굳이 기존 인프라를 버려가면서까지 기술을 바꿀 이유가 없다"며 "사업적인 측면을 고려하면 당연한 수순"이라고 설명했다.

■ HBM4용 본딩 기술의 향방, '제덱' 협의서 갈린다

이와 관련 업계의 시선은 '제덱(JEDEC)'에 쏠리고 있다. 제덱은 반도체 표준 규격을 제정하는 민간표준기구다. HBM4와 관련한 표준도 이 곳에서 논의되고 있다.

현재 제덱에서는 HBM4의 높이를 720마이크로미터와 775마이크로미터 중 하나를 채택하는 방안이 검토되고 있는 것으로 파악됐다. 표준이 775마이크로미터로 정해지는 경우, 기존 본딩 기술로도 충분히 16단 HBM4를 구현 가능하다는 게 업계 전언이다.

해당 표준안을 정하는 주체로는 메모리 공급사는 물론, HBM의 실제 수요처인 팹리스들도 포함돼 있다. 삼성전자·SK하이닉스·마이크론 등 메모리 3사는 공급사 입장 상 775마이크로미터를 주장한 것으로 전해진다.

관련기사

- 삼성전자, HBM4서 '역전' 노린다…로직다이 공정 고도화 추진2023.12.26

- SK하이닉스 "HBM4 본격 개발…내년 하반기 CXL 상용화"2023.12.21

- AMAT, 첨단 패키징용 하이브리드본딩·TSV 기술 선봬2023.07.18

- SKH가 게임 체인저로 꼽은 '이 기술' …3D D램·400단 낸드서 쓴다2024.01.31

다만 일부 참여 기업이 이견을 제시하면서, 1차 협의는 명확한 결론없이 종료됐다. 현재 업계는 2차 협의를 기다리는 상황이다. 이 협의의 향방에 따라 HBM4를 둘러싼 패키징 생태계의 방향성이 정해질 가능성이 유력하다.

업계 관계자는 "앞으로의 HBM 로드맵을 고려하면 하이브리드 본딩이 중장기적으로 가야할 길이라는 점에는 업계의 이견이 없을 것"이라면서도 "HBM4 자체만 놓고 보면 기존 본딩을 그대로 적용할 수 있는 가능성이 열려 있어, 각 메모리 공급사들이 촉각을 곤두세우는 분위기"라고 밝혔다.