삼성전자 파운드리 3나노미터(nm) 공정이 처음 적용된 반도체가 최근 상용화에 도달한 것으로 확인됐다. 3nm는 현재 양산이 가능한 공정 중 가장 최선단에 속하는 영역으로, 삼성전자의 미래 파운드리 시장 경쟁력을 좌우할 핵심 지표로 꼽힌다.

18일(현지시간) 반도체 전문 조사기관 테크인사이츠는 삼성전자 3nm GAA(게이트-올-어라운드) 공정이 적용된 반도체의 내부를 분석한 자료를 발간했다.

앞서 삼성전자는 지난해 6월 말 세계 최초로 3nm GAA 공정을 양산한다고 밝힌 바 있다.

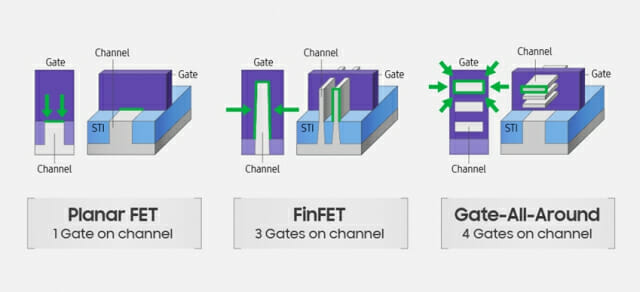

GAA는 반도체를 구성하는 트랜지스터에서 전류가 흐르는 채널 4개면을 모두 감싸는 기술이다. 기존 3개면을 감싸는 핀펫(FinFET) 구조 대비 데이터 처리 속도, 전력 효율성 등을 높일 수 있다.

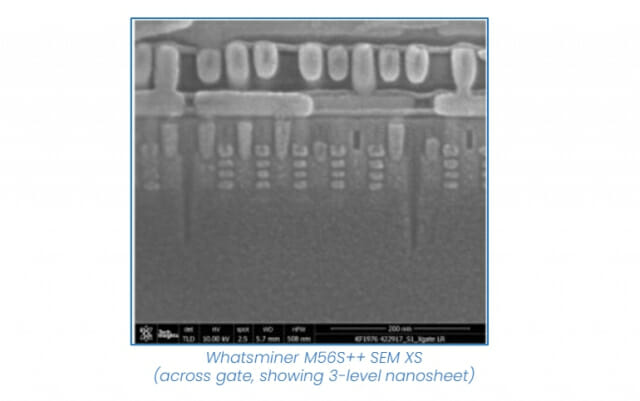

동시에 삼성전자는 채널을 얇고 넓은 모양의 나노시트(Nanosheet) 형태로 구현한 'MBCFET' GAA 구조도 적용했다. 나노시트를 활용하면 기존에 쓰이던 나노와이어 대비 채널·게이트 간 접합면을 넓힐 수 있어, 전류를 더 세밀하게 조절할 수 있게 된다.

당시 삼성전자는 3nm GAA 공정이 적용될 첫 제품과 고객사에 대해서는 밝히지 않았다. 다만 업계는 삼성전자가 중국 소재의 암호화폐 채굴용 시스템반도체 업체로부터 첫 수주를 받은 것으로 파악한 바 있다.

테크인사이츠 역시 이번에 발간한 자료에서 "중국 시스템반도체 업체의 최신 칩으로부터 삼성전자의 3nm GAA 상용화 사례를 첫 확인했다"고 밝혔다.

해당 제품은 마이크로BT가 올해 5월 공개한 '왓츠마이너(Whatsminer) M56S++'의 내부 칩셋다. 마이크로BT는 중국 주요 암호화폐 채굴 전문업체 중 하나로, 채굴용 칩을 개발하는 판세미(Pansemi) 등을 자회사로 두고 있다.

3nm GAA 공정은 삼성전자의 첨단 파운드리 경쟁력을 가늠하는 핵심 요소로 꼽힌다. 주요 경쟁사인 대만 TSMC는 삼성전자보다 6개월가량 늦은 지난해 말부터 3nm 공정 양산에 나섰다. TSMC는 해당 공정에서 여전히 핀펫 구조를 고수했다. TSMC가 GAA 공정을 적용하는 것은 2025년 양산을 앞둔 2nm부터다.

때문에 업계는 삼성전자가 GAA에 대한 '선행 학습'을 먼저 거쳐, 3nm 이하 첨단 파운드리 분야에서의 기술력을 빠르게 안정화할 수 있을 것으로 기대하고 있다.

관련기사

- IBM, 클라우드 서비스에 자체 AI칩 활용 고려…"삼성 파운드리와 협력"2023.07.13

- 삼성전자 파운드리, 2025년 2나노·GaN 공정 시대 연다2023.06.28

- 삼성 파운드리, IP 기업과 협력 확대…AI·HPC 고객 확보 전략2023.06.14

- 삼성 1분기 파운드리 점유율 12.4% '뒷걸음'...TSMC와 격차 더 벌어져2023.06.13

삼성전자도 올 1분기 실적발표 컨퍼런스 콜에서 "3nm GAA 공정을 안정적인 수율로 양산하고 있고, 2세대 공정 역시 1세대 경험을 토대로 차질 없이 개발 중"이라고 자신감을 드러낸 바 있다.

삼성전자의 2세대 3nm GAA 공정 양산 목표 시점은 2024년이다. 2025년에는 TSMC와 마찬가지로 2nm 공정 양산에도 진입할 예정이다.