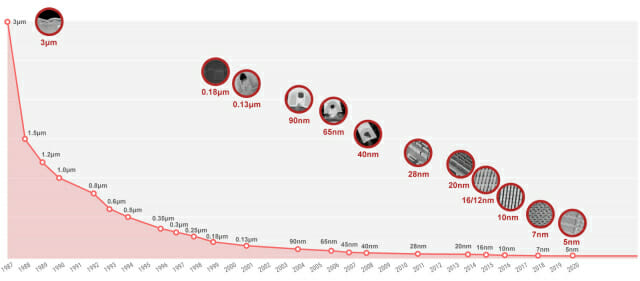

그동안 반도체 공정평가 기준으로 쓰였던 나노미터(nm) 단위 공정 미세도에 대해 '다른 기준이 필요하다'는 업계의 목소리가 끊이지 않고 있다.

트랜지스터 길이를 기준으로 한 공정 명칭은 2차원 평면 트랜지스터에서는 유효했다.

그러나 2010년 이후 3차원 핀펫(FinFET) 트랜지스터가 등장하며 공정 앞에 붙은 숫자와 실제 트랜지스터 길이가 일치하지 않는 현상이 발생하기 시작한 것이다.

이 때문에 최근 반도체 업계에서는 공정의 진척도를 평가하는 새로운 기준이 필요하다는 주장이 잇따라 제기되고 있다.

칩 단위 면적당 트랜지스터 밀집도, 와트 당 성능 등이 주요한 후보로 거론된다. 그러나 두 가지 기준 모두 반도체 특성을 온전히 보여주지 못한다는 맹점이 있다는 지적도 있다.

■ 3차원 트랜지스터 등장하면서 공정 진척 평가 더 복잡해

지금까지 TSMC, 인텔, 삼성전자 등 글로벌 반도체 업체들이 공정의 미세도를 나타내는 데 사용했던 것은 트랜지스터에서 전자의 흐름을 제어하는 게이트의 길이다.

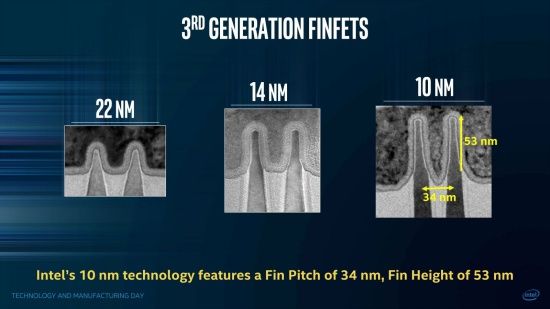

게이트의 길이를 줄일 수록 같은 면적 안에 더 많은 트랜지스터를 넣을 수 있기 때문이다. 이 때문에 많은 반도체 회사들은 트랜지스터 게이트의 길이를 기준으로 공정의 진척도를 나타냈다. 그러나 2010년 이후 3차원 구조로 구성된 핀펫(FinFET) 트랜지스터가 등장하며 이런 기준에 맹점이 생기기 시작했다.

기존 트랜지스터는 게이트가 펼쳐져 있었지만 이를 3차원 구조로 접으면서 정확한 길이 측정이 힘들어졌다. 공정 앞에 붙은 숫자와 실제 트랜지스터 길이가 일치하지 않는 현상이 발생하기 시작한 것이다.

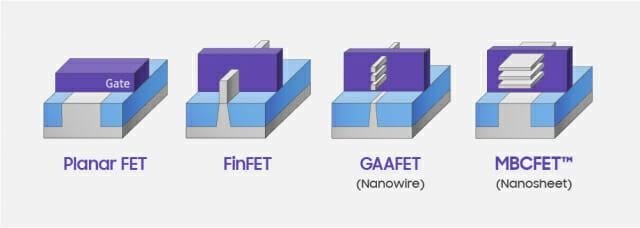

여기에 앞으로 등장할 게이트올어라운드(GAA) 방식 트랜지스터도 문제를 더 복잡하게 만든다.

GAA 트랜지스터는 트랜지스터 내부 게이트의 모든 면을 감싸고 이를 수직으로 쌓아 올리는 방식으로 만들어진다. 이 중 한 층만 측정 기준으로 삼을 것인지, 아니면 여러 층을 면적으로 삼을 것인지에 따라 공정의 진척도 평가는 달라질 수 있다.

■ 반도체 업계도 나노미터 기준에 문제 제기

반도체 업계에서는 이미 수 년 전부터 나노미터(nm) 기준으로 각 제조사(파운드리)의 공정 우위를 따지는 것이 무의미하다는 회의론이 나오고 있다.

지난 해 5월엔 미국 MIT, 스탠포드, UC버클리와 대만 TSMC 연구진들이 논문을 통해 "그동안 반도체 회사들은 트랜지스터 게이트의 길이가 실제로 줄어들지 않았지만 그와 비슷한 성능 향상이 있다는 이유로 공정 명칭을 적용해 왔다"고 지적했다.

필립 웡 TSMC 연구부문 부사장은 2019년 반도체 업계 행사인 '핫칩스 31' 기조연설에서 "오늘날 이런 (공정 앞에 붙는) 숫자는 그저 숫자이며 자동차 모델명처럼 다음 공정을 가리킬 뿐이다. 반도체 공정 이름과 실제 내용물을 혼동하지 말자"고 발언하기도 했다.

■ "단위 면적당 트랜지스터 갯수로 우수성 따지자"

이 때문에 앞으로는 나노미터 대신 반도체 공정의 진척도를 평가하는 새로운 기준이 필요하다는 의견이 나오고 있다. 가장 유력한 것은 바로 단위 면적(제곱밀리미터) 당 트랜지스터 갯수다.

같은 면적 안에 더 많은 트랜지스터를 넣을 수록 더 우수한 성능을 낼 수 있다는 논리다. 미국 MIT, 스탠포드, UC버클리와 대만 TSMC 연구진들은 이에 더해 메모리부 집적도, 트랜지스터와 메모리 연결부 등 총 세 가지 항목으로 구성된 측정법을 제안하기도 했다.

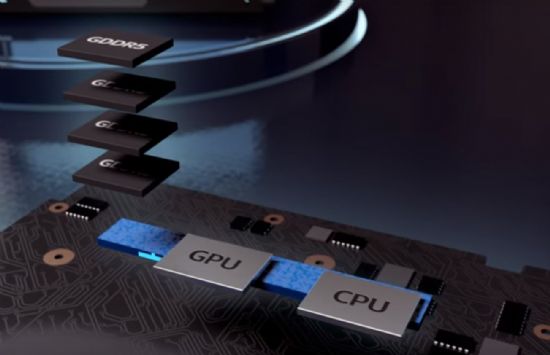

그러나 현재 반도체 발전 방향은 여러 공정에서 생산된 서로 다른 반도체를 연결해 필요한 기능을 구현하는 방식으로 나아가고 있다. 제공하는 기능이 과거보다 더 복잡해지며 한 칩에 모든 것을 넣을 수 없게 됐기 때문이다.

예를 들어 A 회사에서 생산한 프로세서와 B 회사에서 생산한 그래픽칩셋을 결합해 하나의 제품으로 만들 수 있다.

이 때는 단위 면적을 전체 칩으로 볼 것인지, 혹은 각 칩마다 따로 볼 것인지, 또 프로세서와 그래픽칩셋의 집적도를 따로 계산한 다음 평균을 내야하는지 등 복잡한 문제가 발생한다.

■ ARM "집적도는 무의미...와트 당 성능이 중요"

트랜지스터 집적도 대신 다른 기준을 적용해야 한다는 의견도 나왔다.

롭 아이트켄 ARM 기술부문 펠로우는 12일(영국 현지시간) 공식 블로그 기고문을 통해 "프로세서의 성능 향상 판단 기준을 와트당 성능(Performance per Watt)으로 측정해야 한다"는 주장을 내놨다.

롭 아이트켄은 "최신 프로세서 디자인이 연산 효율성을 중요한 성능 향상 지표로 삼고 있는 만큼 와트당 성능이 새로운 패러다임이 될 것"이라고 주장했다. 같은 작업을 처리하는 데 얼마나 많은 전력을 쓰는지를 기준으로 삼자는 의미다.

관련기사

- 인텔코리아 "매년 새 공정 프로세서·파운드리에 적용"2021.08.10

- ARM "프로세서, 와트당 성능으로 측정해야"2021.07.15

- [컴퓨텍스2021] AMD '3D 칩렛' 공세 속 수세 몰린 인텔...퀄컴 PC '눈길'2021.06.04

- 인텔, 프로세서 설계·제조 분리할까2021.01.05

문제는 와트 당 성능을 측정할 수 있는 기준이 없다는 것이다. 프로세서나 칩마다 처리할 수 있는 명령어와 처리 방식이 모두 다르며 가장 높은 효율을 낼 수 있는 작업이 서로 다르다.

결국 현재는 나노미터 기반 숫자를 이용한 공정 표기법 이외에 뾰족한 대안이 없는 상황이다.