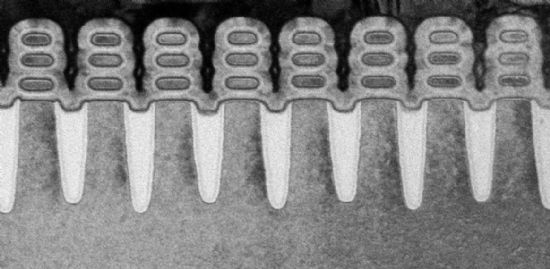

IBM은 삼성전자, 글로벌파운드리(GF)와 함께 업계 최초로 5나노미터(nm) 반도체 제조가 가능한 실리콘 나노시트(nanosheet) 트랜지스터 생산 공정 개발에 성공했다고 5일 밝혔다.

삼성전자, 글로벌파운드리가 참여하는 IBM리서치연합(IBM Research Alliance)은 2년 전 200억개의 트랜지스터를 집적할 수 있는 7나노 테스트노드칩 개발에 성공한데 이어, 이번에 손톱만한 크기의 칩에 300억개의 트랜지스터를 집적할 수 있는 기술 개발에도 성공했다.

7나노 테스트 노드와 200억개 트랜지스터를 제작하는데 사용된 극자외선(EUV) 노광 기술이 이번 나노시트 트랜지스터 아키텍처에도 적용됐다. 이 기술을 통해 단일 제조 공정이나 칩 설계 상에서 나노시트 너비를 지속적으로 조정할 수 있다.

이에 따라 기존 핀펫 트랜지스터 아키텍처에서는 전류가 흐르는 핀높이의 제약 때문에 불가능했던 특정 서킷의 성능과 전력의 미세한 조정도 가능해졌다. 핀펫 아키텍처로도 5나노 칩을 구현할 수 있지만 단순히 핀 사이 간격을 줄이는 것으로 추가적인 성능을 위한 전류 증가는 기대하기 힘들다.

IBM리서치연합은 7나노 공정 기술을 뛰어넘기 위해 기존 연구에는 핀펫(FinFET) 아키텍처 대신 실리콘 나노시트 스택을 사용한 트랜지스터 디바이스 구조를 도입했다. 나노시트 기반의 5나노 기술을 사용하면 현재 최신 10나노 칩과 비교했을 때 동일한 전력 소모 시 성능이 40% 향상되고, 동일한 성능에서는 전력 소모량이 75% 감소한다.

IBM은 이러한 발전을 통해 인공지능(AI) 시스템과 가상 현실, 모바일 기기에 대한 미래의 요구사항을 더 빠르게 충족시킬 수 있을 것으로 내다보고 있다.

관련기사

- "2020년 4나노까지"…삼성 파운드리 로드맵2017.06.05

- 가트너 “지난해 세계 반도체 매출 2.6% 증가”2017.06.05

- 반도체協, 중소 기업과 대학으로 인재 찾아 나선다2017.06.05

- 삼성전자 DS부문 조직개편…파운드리 분리2017.06.05

IBM리서치연합은 "트랜지스터 집적도 향상은 클라우드를 통해 제공되는 인공지능을 포함한 코그너티브(인지) 컴퓨팅, 사물인터넷(IoT) 및 기타 데이터 집약적 애플리케이션의 성능 향상으로 이어질 수 있다"면서 "또 전력 효율성 개선으로 스마트폰과 기타 모바일 제품의 배터리 지속시간이 현재 사용되고 있는 기기들과 비교해 최대 2~3배 늘어나게 된다"고 설명했다.

이번 연구는 뉴욕주립대(SUNY) 폴리테크닉 연구소 나노스케일과학공학대학의 나노테크 컴플렉스에서 진행됐다. IBM 리서치는 나노시트 반도체 기술에 대한 연구를 10년 이상 진행해왔다. 지난 2014년 IBM은 향후 5년 간 칩 연구 개발에 30억 달러를 투자하겠다고 발표한 바 있다.