국내 IP(설계자산) 업체 퀄리타스반도체가 UCIe(Universal Chiplet Interconnect Express) 표준 ver2.0을 지원하는 IP개발을 성공적으로 완료했다고 10일 밝혔다.

이번에 개발된 UCIe PHY IP는 송수신 채널 총 32개를 통해 최대 512Gbps(56GB/s) 전송 속도를 제공하며 고대역폭·저지연 특성을 구현해 칩렛(Chiplet) 간 고속 데이터 전송에 최적화된 성능을 발휘한다.

특히, 32개 채널 전체의 패키지 전송 트레이스 폭이 약 1mm 수준으로 매우 좁아, 기존 PCI Express 등 고속 인터페이스 대비 월등한 전송 밀도를 제공한다. 이로 인해 해당 IP는 고성능 AI 가속기, 데이터센터용 SoC, 네트워크 및 서버 시스템 등 차세대 고집적 반도체 설계에 필수적인 Die-to-Die 인터커넥트 기술로 주목받고 있다.

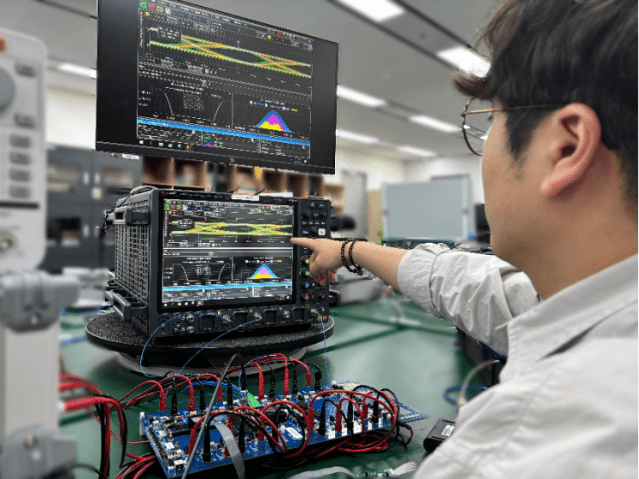

퀄리타스반도체는 단순한 IP 설계를 넘어, 패키지 및 테스트 보드를 직접 설계하고 실리콘 수준에서의 검증까지 독자적으로 수행했다. 고속 측정 기술과 테스트 기반 모델링을 바탕으로, 복잡한 칩 설계 환경에서의 성능 예측 및 품질 확보에 필수적인 종단 간 검증 체계를 사내 랩을 통해 구축한 점이 강점이다.

또한 고속,고집적 인터페이스의 구현을 위해, 국내 최고 수준의 패키지 기술력을 보유한 하나마이크론과 협력해, UCIe 전용 스탠다드 및 어드밴스드 패키징 기술을 구현했다. 이번 프로젝트에서도 높은 난이도의 설계 요건을 충족하는 실물 패키지를 제조하여 제공함으로써, 설계 사양에 최적화된 결과물을 구현하는 데 성공했다.

UCIe는 다양한 이종 칩렛 간 고밀도 데이터 연결을 가능케 하는 기술로, 기존 인터페이스와는 달리 패키지 및 보드 환경에 최적화된 설계 대응력이 핵심이다.

관련기사

- 퀄리타스반도체, 최신 DSC 1.2a 솔루션 최초 공개2024.12.17

- 퀄리타스반도체, 엣지 AI 반도체 '암바렐라'와 추가 계약2025.01.17

- 퀄리타스반도체, '세계 최초' 2나노 MIPI 솔루션 美 고객사에 공급2024.09.09

- 퀄리타스반도체, AI·자율주행용 칩렛 인터페이스 IP 호환성 검증2024.07.16

이번 IP 개발은 퀄리타스반도체가 주관기관으로 참여 중인 ‘ICT 융합산업혁신기술개발사업 – 인공지능 및 자동차 SoC용 칩렛 인터페이스 IP 개발’ 과제의 일환으로, 2023년부터 수행된 3개년 연구 성과에 기반해 이뤄졌다.

김두호 퀄리타스반도체 대표는 “UCIe는 글로벌 반도체 업계뿐 아니라 많은 고객사들이 높은 관심을 보이는 차세대 칩렛 인터페이스 표준”이라며 “이번 IP는 실리콘 기반 검증을 통해 당사의 기술력과 상용 공정에서의 구현 가능성을 입증한 대표적 성과로, 앞으로도 고객 맞춤형 고속 인터페이스 솔루션을 지속 확대해 나갈 계획”이라고 말했다.