인텔 파운드리는 IEEE 국제전자소자학회(IEDM) 2024에서 트랜지스터 스케일링, 패키징, 신소재 등 연구 성과를 공개했다.

인텔은 기존 구리 배선 기반 공정의 한계점으로 꼽히던 정전 용량 증가와 누설 전류, 간섭 등을 해결할 수 있는 새로운 소재 '감극성 루테늄'을 제시했다.

이 기술은 박막 저항 특성을 통해 25nm 이하의 피치에서도 정전 용량을 최대 25%까지 감소시킨다.

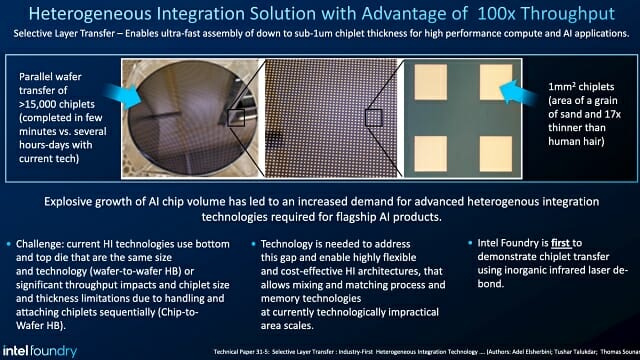

새로운 이기종 패키징 방식인 '선택적 층전송'(SLT) 기술은 기존 칩-웨이퍼 본딩 기술을 대신해 초박형 칩렛을 기판 위에 부착하는 방식이다. 소형화와 성능 향상, AI 응용프로그램이 요구하는 높은 처리량과 유연한 아키텍처 설계를 지원한다.

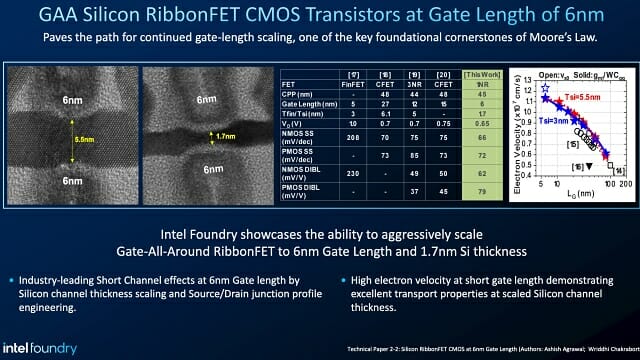

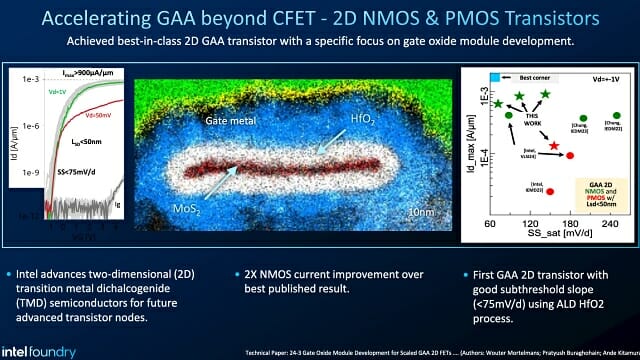

인텔은 GAA(게이트-올-어라운드) 스케일링을 넘어서는 새로운 트랜지스터 기술도 공개했다. 실리콘 리본펫 CMOS는 6nm 길이에서 뛰어난 쇼트 채널 효과를 제공하며, 무어의 법칙을 지속할 수 있는 기반을 마련한다.

또한, 2차원(평면) FET를 위한 게이트 산화물 모듈을 개발하며 트랜지스터 성능을 극대화했다.

IEDM 2024에서는 업계 최초로 300mm GaN-on-TRSOI 기판을 활용한 강화 모드 GaN MOSHEMT 기술도 소개됐다. 이 기술은 전력 및 RF 전자 장비에서 신호 손실을 줄이고, 고온 및 고전압 환경에서도 안정적인 성능을 제공한다.

관련기사

- 인텔 이사회에 ASML·마이크로칩 전 CEO 합류2024.12.06

- 흔들리는 인텔, 차기 CEO 누가 될까..."립부탄 유력"2024.12.05

- 인텔, 데스크톱용 아크 2세대 GPU 'B580' 공개2024.12.03

- 인텔-美 상무부, 15.9조 규모 반도체법 보조금 최종 합의2024.11.26

산제이 나타라잔 인텔 파운드리 기술 리서치 총괄 수석 부사장은 "이번에 발표한 신기술은 미국 반도체지원법(CHIPS Act) 아래 글로벌 공급망을 강화하고 미국 내 반도체 제조 리더십을 회복하려는 인텔의 노력을 보여주는 사례"라고 밝혔다.

이어 "우리의 연구는 반도체 산업의 미래를 설계하는 중요한 이정표가 될 것”이라고 덧붙였다.