SK하이닉스가 최근 업계 최선단 공정 기반의 D램을 가장 먼저 개발하는 성과를 거뒀다. 회사는 이에 그치지 않고 3D 셀, 이종접합 등 기술 혁신으로 차세대 D램 시대에 대응한다는 전략이다.

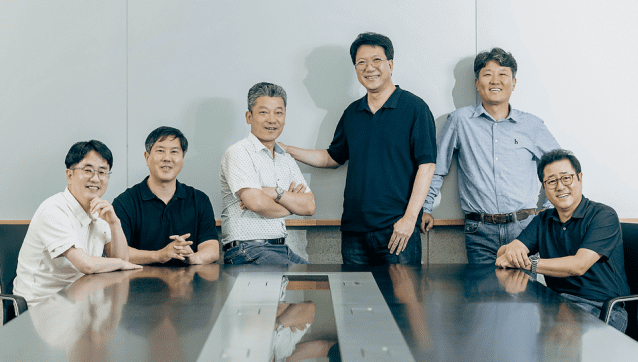

SK하이닉스는 지난달 29일 10나노급 6세대(1c) 16Gb(기가비트) DDR5 D램을 개발한 주역들과 좌담회를 진행했다고 10일 밝혔다.

해당 자리에는 1c 기술 개발을 주도한 오태경 SK하이닉스 부사장(1c Tech TF), 조주환 부사장(DRAM 설계), 조영만 부사장(DRAM PI), 정창교 부사장(DRAM PE), 손수용 부사장(개발 TEST), 김형수 부사장(DRAM AE)이 참석했다.

1c 기술은 10나노대 초반의 극미세화된 메모리 공정 기술이다. 1c 기술을 적용한 DDR5의 동작 속도는 8Gbps(초당 8기가비트)로 이전 세대인 1b DDR5보다 11% 빨라졌으며, 전력 효율은 9% 이상 개선됐다.

성능뿐만 아니다. SK하이닉스는 EUV 공정에 신소재를 개발해 적용하는 한편, 설계 기술 혁신을 통해 공정 효율을 극대화했으며 원가 절감까지 이루어냈다.

SK하이닉스는 1c 개발 가속화를 위해 이미 우수성이 증명된 1b 플랫폼을 확장하는 방식으로 개발하는 전략을 선택하고, 기존의 3단계(테스트, 설계, 양산 준비) 개발 방식을 2단계(설계, 양산 준비)로 효율화했다.

오태경 부사장은 "1c 기술 개발을 총괄한 1c Tech TF의 가장 큰 목표는 ‘1등 개발’이었다"며 "커패시터(Capacitor) 모듈과 같은 고난도의 기술 요소를 양산 공정에서 바로 개발하는 방식을 택한 덕분에 전세대 제품 대비 2개월이나 단축해 1c 기술 개발에 성공할 수 있었다"고 설명했다.

정창교 부사장은 "공정이 미세화되면서 과거와는 다른 특성들이 더 중요해지고, 이로 인해 수율 저하 등 문제가 발생할 수 있다"며 "1c 기술에서 주요 성능의 수준을 높이는 트리밍 기술을 활용해 수율과 품질을 확보했다"고 밝혔다.

트리밍이란, 반도체 설계 변경 없이 전자식 퓨즈(eFuse)를 활용해 성능을 상향시키는 기술을 뜻한다.

나아가 SK하이닉스는 1c 이후의 차세대 D램 제품에서도 선두를 유지하기 위한 전략을 구상 중이다.

관련기사

- SK하이닉스, 세계 최초 10나노급 6세대 D램 '1c DDR5' 개발2024.08.29

- 삼성전자, '1b D램' 양산에 사활…수율 잡을 TF 가동2024.06.11

- SK하이닉스 "HBM3E 수율 80% 근접"…업계 예상 뛰어넘어2024.05.22

- 삼성·SK, 차세대 HBM4 경쟁력 승부처 '1c D램' 주목2024.05.17

조영만 부사장은 "1c 기술을 넘어 D램 기술은 점점 더 미세화될 것이고, 특히 10나노 아래 한 자릿수 기술로 넘어가는 시점이 오면 기존 방식으로는 한계가 있을 것"이라며 "이를 극복하기 위해서는 소재 및 장비의 성능을 극대화하는 것뿐만 아니라 2D 셀에서 3D 셀로의 구조 변화, 이종접합 등과 같은 기술 혁신 역시 필요하다"고 강조했다.

한편 SK하이닉스는 연내 1c DDR5의 양산 준비를 마치고 내년부터 시장에 제품을 본격 공급할 계획이다.