대만 TSMC는 내년에 가격이 최대 8.5% 낮아진 '가성비' 4나노미터(nm) 공정 서비스를 제공할 예정이다. 이를 통해 TSMC는 파운드리 고객사를 확대해 삼성전자와 인텔과의 경쟁에서 선두를 유지한다는 전략이다.

TSMC는 최근 미국 캘리포니아 주 산타클라라에서 열린 'TSMC 2024 테크놀로지 심포지엄'에서 4나노 공정 'N4C' 기술을 공개했다.

N4C은 기존 'N4P' 공정을 개선한 기술로 5나노급 노드 제품군에 속한다. N4C는 기존 공정보다 표준 셀, S램 셀 재설계, 일부 설계 규칙 변경, 마스킹 레이어 수 감소 등의 개선을 통해 생산 복잡성이 감소했다. 또 비용도 기존 4~5나노 공정 대비 최대 8.5%의 생산비용을 절감할 수 있다. 또한 N4C는 N4P와 동일한 웨이퍼 결함 밀도에도 다이 면적 감소로 더 높은 수율을 제공한다. TSMC는 내년부터 N4C 공정에서 칩을 대량 양산할 예정이다.

TSMC의 비즈니스 개발 담당 케빈 장(Kevin Zhang) 부사장은 "5나노(N5)에서 4나노(N4)로의 전환으로 4% 밀도 향상을 달성했고, 트랜지스터 성능도 지속적으로 개선되고 있다"라며 "고객은 N4C 공정을 통해 비용을 절감할 수 있다"고 말했다.

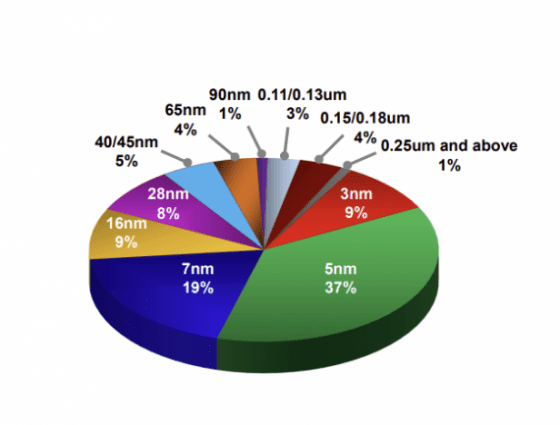

첨단 공정에 속하는 4나노 공정은 수익성이 높다. 올해 1분기 기준 TSMC 매출에서 4~5나노 공정이 차지하는 비율은 37%로 회사 매출의 가장 많은 부분을 차지한다.

4~5나노 공정의 주요 고객사로는 엔비디아, AMD, 애플 등이 대표적이다. 엔비디아가 지난 3월 발표한 AI 가속기 B100 GPU도 TSMC 4나노 공정에서 생산된다.

반면 TSMC의 가장 첨단 공정인 3나노의 매출 비중은 9%로 아직 미비하다. 3나노 공정은 캐파가 아직 많지 않을뿐더러 스마트폰용 AP 등에 주문이 집중돼 있기 때문이다. 또 3나노 공정은 4나노 공정보다 약 1.8~2배 비싼 것으로 알려진다.

TSMC는 가격을 낮춘 4나노 공정을 제공함으로써 팹리스 고객사에 가격 부담을 낮추고, 삼성전자와 인텔과 고객 경쟁에서 우위를 차지할 것으로 기대한다.

관련기사

- 5나노 이하 최선단 파운드리, AI·애플 효과로 비중 확대2024.04.11

- [단독] 인텔, 韓 파운드리 공략...삼성 출신 부사장 배치2024.03.29

- SK하이닉스, TSMC 테크 행사서 'HBM·패키징 협력 관계' 강조2024.04.25

- SK하이닉스, TSMC와 6세대 HBM 개발...내후년 양산2024.04.19

반도체 업계에 따르면 통상 삼성전자의 파운드리 가격은 같은 공정에서 TSMC 보다 저렴하다. 파운드리 후발주자인 삼성전자는 TSMC와 경쟁을 위해 고객에게 가격 부담을 낮추는 전략을 펼친 것이다. 그러나 TSMC가 가성비 높은 4나노 공정 서비스를 시작함에 따라 고객 유치에 유리해질 가능성이 높아졌다.

한편, TSMC는 이번 심포지엄에서 1.6나노(16A) 공정 기술 로드맵도 처음으로 공개했다. TSMC는 2026년 하반기부터 1.6나노 공정으로 반도체를 생산할 계획이라고 밝혔다. 경쟁사인 인텔은 올해 말부터 1.8나노(18A) 공정 양산에 착수한다. 삼성전자는 내년에 2나노(SF2), 2027년에는 1.4나노 공정을 양산할 예정이다.