미국 인텔과 대만 UMC가 12나노미터(mn, 10억분의 1m) 공정에서 파운드리 협력에 나선다. 이번 협력은 파운드리 재진출을 선언한 인텔과 대만에서 파운드리 2위 업체인 UMC가 손잡는다는 점에서 업계의 주목을 받는다. 양사의 파운드리 협력이 삼성전자에 어떤 영향을 미칠지 관심이 쏠린다.

반도체 업계 전문가들은 삼성전자가 성숙(레거시) 공정보다는 7나노 이하의 첨단(어드밴스드) 공정에 주력하고 있기 때문에 인텔과 UMC의 협력이 파운드리 사업에 단기적으로 큰 영향을 받지 않을 것으로 평가했다.

다만, 삼성전자가 10나노대 공정에서도 파운드리 사업을 하고 있다는 점에서 장기적으로 인텔에 고객사를 빼앗길 가능성이 우려된다는 목소리도 나온다. 인텔과 UMC가 12나노 공정 외에도 협력을 확장할 가능성이 있기에 양사의 동맹을 계속 주목해야 한다는 의견이다.

인텔·UMC 12나노 파운드리 동맹…2027년부터 생산

인텔과 UMC는 지난 25일(현지시간) 12나노 공정 파운드리 협력을 발표했다.

인텔은 3차원 트랜지스터 구조 핀펫(FinFET) 공정 기술을 제공하고, UMC는 그동안 레거시 파운드리 공정에서 쌓은 설계자산(IP)과 PDK(공정개발킷)을 지원한다. 양사는 애리조나주 챈들러에 위치한 기존 인텔 팹22와 팹32에서 2027년부터 12나노 공정으로 반도체를 생산할 계획이다.

김형준 차세대지능형반도체 사업단장은 “인텔은 수익성이 높은 인텔20A(2나노급), 18A(1.8나노급) 등 초미세 공정 개발에 주력하고 있는데, UMC로부터 12나노 IP를 공급받게 되면서 파운드리 스펙트럼을 넓힐 수 있게 됐다”며 “UMC는 파운드리 노하우를 인텔에 제공하고, 인텔은 첨단 공정 기술을 제공해 상호 보완할 것으로 보인다”고 설명했다.

결과적으로 인텔은 이번 협력을 통해 IDM에서 파운드리 비즈니스 모델로 수월하게 전환하면서, 2나노 및 3나노와 같은 첨단 프로세스 개발에 더 집중할 수 있게 됐다.

그동안 22나노 및 28나노 공정에 주력했던 UMC는 과도한 투자비용 부담 없이 10나노대 공정에서 필수인 핀펫 기술을 확보할 수 있게 됐다. UMC는 2017년부터 14나노 공정을 개발해 왔지만 아직 대량 생산에 이르지 못했고, 12나노 공정은 아직 R&D 단계에 머무는 수준이었기 때문이다. 아울러 UMC는 인텔의 미국 팹을 공동으로 관리하면서 글로벌 시장에서 입지를 강화할 것으로 기대된다.

시장조사업체 트렌드포스는 “양사가 인텔의 기존 팹을 활용함으로써 생산 장비 재배치, 배관 설치 등에 대한 투자 비용을 80% 절감할 수 있게 됐다. UMC는 인텔의 파운드리 비즈니스 협상을 돕는 데 중요한 역할을 할 전망”이라며 “앞으로 이 파트너십이 순조롭게 진행된다면 인텔이 UMC와 추가로 1Xnm 핀펫 시설을 공동 관리하면서 잠재적으로 아일랜드의 팹24 및 오레곤의 D1B, D1C로 확장을 고려할 수도 있다”고 내다봤다.

삼성전자, 미세공정 파운드리에 주력...양사 동맹 예의주시 필요

삼성전자는 수익성이 높은 7나노 이하의 첨단 공정에 주력하고 있지만, 10나노대 공정에서도 파운드리 사업을 하고 있기에 인텔과 UMC의 협력에 경계심을 갖고 예의주시해야 한다는 의견이 나온다.

삼성전자 미국 오스틴 공장은 14∼65나노 공정을 기반으로 모바일 애플리케이션(AP), 솔리드스테이트드라이브(SSD) 컨트롤러, 디스플레이드라이버 IC(DDI), CMOS 이미지센서, RF 칩 등 IT용 반도체를 주로 생산하고 있다. 인텔이 2027년 12나노 공정에서 반도체를 생산을 시작하면, 삼성전자는 고객사 이탈에 대한 우려가 따를 수밖에 없다.

유재희 반도체공학회 부회장(홍익대 전자전기공학부 교수)은 “삼성전자가 10나노대의 매출을 공개하고 있지 않아서 알 수는 없지만, 이 시장 또한 놓칠 수 없는 시장인 것은 분명하다”라며 “5나노 이하 공정이 부가가치가 높더라도 모든 칩이 2나노, 3나노 공정이 필요한 것은 아니며, 삼성이 2나노 3나노 공정에서 많은 수주를 한다는 보장이 없다. 인텔과 UMC의 협력의 영향은 정도의 문제일 뿐, 영향을 안 받는다고 볼 수는 없을 것”이라고 말했다.

유 부회장은 이어 “인텔이 2나노, 3나노 공정에 막대한 투자를 하면서 이번에 UMC와 협력한다는 것은 현금 흐름을 위해서 어느 정도 10나노대에서 사업을 일으켜 보겠다는 의도가 확실해 보인다”고 덧붙였다.

김형준 차세대지능형반도체 사업단장도 “삼성전자는 40나노 60나노에는 리소스가 한정돼 있어서 과감하게 포기하고 20나노 및 10나노 이하에 주력하고 있다. 현재 삼성전자의 파운드리 사업은 미세공정에 초점이 맞춰져 있지만, 10나노대 사업도 중요하기에 인텔을 신경써야 할 것”라며 “경쟁에서 누가 캐파를 많이 갖고, 수율을 높이느냐가 관건일 것”이라고 말했다.

반면, 양사의 협력이 삼성전자의 사업에 크게 영향을 주지 않을 것이라는 의견도 나온다.

관련기사

- 세계 1위 TSMC가 내다 본 올해 파운드리 시장 전망은2024.01.19

- 한진만 삼성전자 "AI 시대, 파운드리 메모리 시너지 본격화…주문 늘었다"2024.01.12

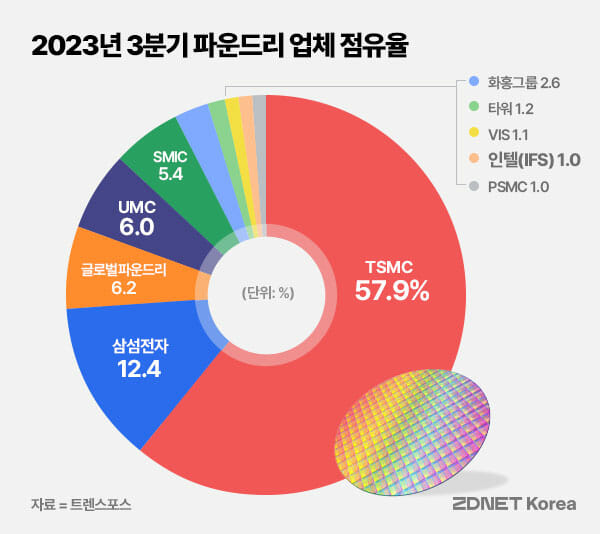

- 파운드리 매출 다시 회복세…삼성·TSMC 격차는 더 벌어져2023.12.06

- 삼성 파운드리 "양산 고객사 11년만에 5배 증가 전망"2023.11.08

황철성 서울대학교 전자재료공학 석좌교수는 “삼성전자는 선단 노드에서 TSMC와 경쟁하기에도 바쁘다. 레거시 노드는 삼성이 서포트할 수 없고 이윤이 많이 안남기 때문에 할 이유도 없다고 본다. TSMC가 레거시 노드까지 다 서비스하는 이유는 오래전부터 해온 사업이고, 팹을 놀리는 것보다 돌리는 것이 낫다고 판단하고 있기 때문일 것”이라고 설명했다.

이어 그는 “삼성전자 파운드리 사업은 전자 반도체 사업에 30%도 안 되고, 그 중에서 레거시 반도체 생산 비중은 매우 적다. 반면 인텔은 CPU 만들다가 파운드리로 전환하는 과정에서 TSMC와 경쟁하기 위해 다양한 포트폴리오를 갖추려고 하는 것”이라며 “그러다 보니 직접 12나노 공정 기술을 개발하는 것은 비용 부담이 돼, UMC와 협력한 것으로 보인다”고 말했다.