인텔과 대만 UMC(聯華電子)는 25일(미국/대만 현지시간) 12나노급 반도체 생산 공정을 공동 개발한다고 밝혔다.

양사가 개발하는 12나노급 새 반도체 공정은 인텔이 가지고 있는 3차원 트랜지스터 구조 '핀펫'(FinFET)을 활용한다. UMC는 주요 고객사에 12나노급 새 공정용 반도체 개발에 필요한 PDK(공정개발킷)를 공급하고 설계 지원에 나선다.

팻 겔싱어 인텔 CEO는 "이번 제휴는 모바일, 통신 인프라와 네트워킹 등 고성장 분야를 겨냥한 것이며 인텔과 UMC의 파운드리 공정 포트폴리오를 확대하고 인텔 애리조나 시설을 활용한 원활한 고객의 공급을 도울 것"이라고 설명했다.

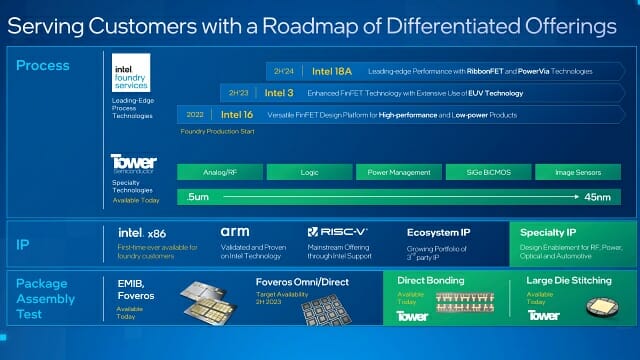

인텔이 2022년 하반기부터 시험 생산에 들어간 '인텔 16' 공정은 2011년 상용화한 22나노미터급 공정을 개선한 것이다. 성능과 전력 소모, 집적도를 향상시켰고 더 적은 마스크와 단순한 백엔드 디자인으로 16nm급 성능을 제공한다는 것이 당시 인텔 설명이었다.

인텔은 지금까지 미세 공정이 반드시 필요하지 않은 자동차나 통신 영역 반도체 생산에 인텔 16 공정을 활용했다. 그러나 성능이나 소비 전력 효율 면에서 불충분하다는 판단을 내리고 한 단계 앞선 새 공정을 개발하기로 한 것으로 보인다.

인텔 14나노급 공정은 수 년간 코어·제온 프로세서 등 핵심 제품 생산을 통해 충분히 성숙됐고 대량 생산도 가능하다. 그러나 이 공정은 그간 내부 제품에만 활용돼 외부 고객사에 제공하기 쉽지 않다.

반면 UMC는 2017년부터 14나노급 공정을 생산하면서 외부 고객사를 다수 확보했고 PDK 등도 갖추고 있다. 그러나 생산 역량은 제한적이다.

UMC는 현재 14나노급 웨이퍼를 대만 타이난 소재 '팹 12A'에서 생산중이지만 월 웨이퍼 처리량은 5만 5천장 가량에 그친다. 이번 양사 협업은 PDK 관련 노하우가 필요한 인텔과 생산 역량 확충을 원하는 UMC의 이해가 일치한 것으로 볼 수 있다.

관련기사

- 인텔 "PC 침체기 끝 보인다...재고 수준 지속 하락"2024.01.26

- 4분기 호실적에도 못 웃는 인텔…1분기 전망 '빨간불'2024.01.26

- 인텔, 2025년 이후 공정 로드맵 언제 내놓나2024.01.25

- 인텔, 美 뉴멕시코 주 패키징 시설 '팹9' 완공2024.01.25

인텔은 "12나노급 새 공정은 미국 애리조나 주 오코틸로 소재 시설인 팹 12·22·32를 활용하며 이를 통해 초기 투자 비용을 크게 줄일 것"이라고 설명했다.

양사는 EDA(전자자동화설계)와 외부 생태계 협력사의 반도체 IP(지적재산권) 강화를 통해 12나노급 새 공정 안착에 주력할 예정이다. 실제 제품 생산은 오는 2027년부터 시작될 예정이다.