삼성전자, TSMC에 이어 인텔도 극자외선(EUV) 기술을 사용해 7나노미터(mn)급 공정으로 반도체 대량생산에 나섰다. 인텔은 당분간 자사 제품 중심으로 첨단 공정 기반의 칩을 생산하지만, 향후 고객사를 확보해 외부 물량도 생산한다는 목표다.

2021년 파운드리(위탁생산) 시장 재진출을 선언한 인텔이 미세공정 시장에서 삼성전자와 TSMC와 본격 경쟁구도에 나선다는 점에서 향후 이들 업체간 고객사 유치를 위한 경쟁이 후끈 달아오를 전망이다.

■ 인텔, 7나노급 공정 양산 시작…2030년 파운드리 2위 목표

인텔은 4일 유럽 아일랜드에 위치한 신규 팹34에서 EUV 기술을 적용한 인텔4(7나노급) 공정으로 14세대 모바일용 중앙처리장치(CPU) '메테오레이크' 양산을 시작한다고 발표했다.

이는 인텔이 대량 제조(high-volume manufacturing, HVM)에 EUV를 사용하는 최초 사례다. 그동안 인텔은 미국 오레곤 팹에서 인텔4 공정 개발과 초기 생산을 담당해 왔다. 인텔 팹34은 내년부터 인텔3(4나노급) 공정 생산을 시작하며, 제온 프로세서 등 차세대 제품 생산도 담당할 예정이다.

인텔4 공정은 인텔이 반도체 생산에 본격적으로 EUV 기술을 사용한다는 점에서 의미가 크다. 7나노미터 이하의 초미세 반도체를 생산하려면 EUV 기술이 필요하다. EUV 노광 기술은 짧은 파장의 극자외선으로 세밀하게 회로를 그릴 수 있고, 회로를 새기는 작업을 반복하는 멀티 패터닝(Multi-Patterning) 공정을 줄일 수 있어 성능과 수율이 향상된다. 또 제품 출시 기간을 단축할 수 있는 게 장점이다.

그동안 파운드리 시장에서 TSMC와 삼성전자만이 EUV 기술을 적용해 칩을 양산해 왔지만, 이번에 인텔이 가세하면서 경쟁구도가 다각화될 것으로 보인다.

다만, 인텔의 7나노급 공정 양산은 경쟁사인 삼성전자와 TSMC 보다 약 4년이 늦춰진 상태다. TSMC와 삼성전자는 일찌감치 각각 2018년, 2019년에 7나노 공정 칩 양산을 시작했고, 양사는 지난해 3나노 공정 양산까지 성공했다.

이에 인텔은 공격적인 파운드리 로드맵을 내놨다. ▲인텔 4(7나노급)/ 2023년 상반기 ▲인텔 3(4나노급)/ 2023년 하반기 ▲인텔 20A(2나노급)/ 2024년 하반기 ▲인텔 18A(1.8나노급)/ 2025년 순으로 공정을 실현한다는 계획이다. 이를 통해 인텔은 2025년 2나노 이하 공정에서 삼성전자와 TSMC를 추월하고, 2030년까지 파운드리 시장 2위로 올라선다는 포부를 밝혔다.

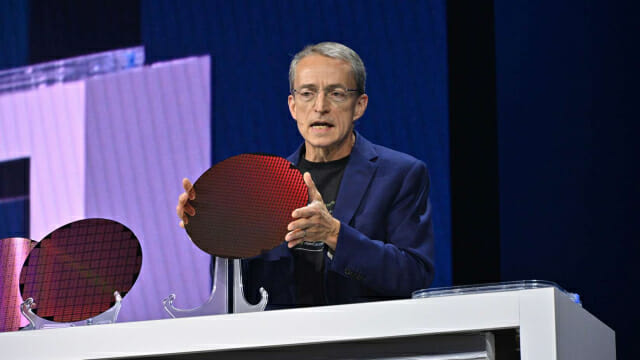

일각에서는 인텔이 아직 3나노도 생산하지 않는 단계에서 단숨에 TSMC와 삼성전자의 역전을 노리기는 현실적으로 어렵다는 의견도 나온다. 이에 대한 반격으로 인텔은 지난 9월 미국 새너제이에서 개최한 '인텔 이노베이션 2023' 행사에서 1.8나노급인 18A 공정 반도체 웨이퍼 시제품을 깜짝 공개하기도 했다.

앞서 인텔은 2021년 파운드리 시장 재진출을 선언하는 ‘IDM 2.0’ 비전을 발표하면서 파운드리 비즈니스를 담당할 인텔 파운드리 서비스(IFS) 사업부를 신설했다. 이후 인텔은 미국, 유럽 등 각 지역에서 반도체 신규 공장 건설에 한창이다. 또 인텔은 지난 6월 ‘IDM 2.0’ 2단계를 발표하며 내년부터 반도체 제조, 기술개발을 한데 모아 ‘제조 그룹’ 사업부로 격상한다고 밝혔다.

삼성전자·TSMC, 2025년 2나노 양산 치열한 경쟁...라피더스 가세

삼성전자와 TSMC 모두 2025년 양산을 목표로 2나노 기술 개발에 박차를 가하고 있다.

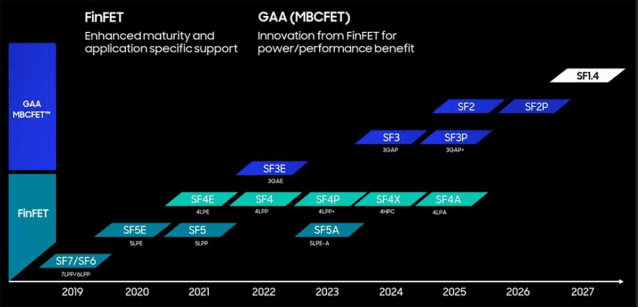

삼성전자는 지난해 6월 세계 최초로 GAA(Gate-All-Around) 구조를 적용한 3나노 양산을 시작한데 이어 내년 2세대 3나노 공정 양산을 준비 중이다. 또 2025년 2나노 공정, 2027년에는 1.4나노 공정으로 칩을 생산한다는 계획도 밝혔다.

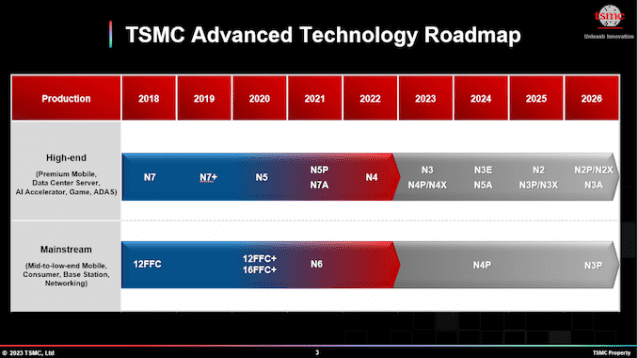

TSMC는 지난해 12월 3나노(3N) 공정 양산을 시작했으며, 내년에 진화된 3나노 공정(N3E), 2025년에 2나노(N2) 공정, 2028년 1나노 공정 양산을 목표로 한다. TSMC는 2나노 양산에 앞서 시제품 생산을 내년 초로 계획했지만, 이를 앞당겨 연내에 소량 생산한다는 전망도 나온다. 이는 삼성전자와 인텔을 견제해 빠르게 고객사를 확보하려는 움직임으로 풀이된다.

관련기사

- 삼성 파운드리, 텐스토렌트 4나노 AI 반도체 만든다2023.10.04

- "파운드리 가동률 반등 시작"…삼성도 실적 개선 기대감2023.10.04

- 3나노 모바일 AP 시대 본격화…파운드리, 고객사 확보에 사활2023.09.14

- 인텔, 타워 세미컨덕터 인수 불발에 '파운드리 협력' 선회2023.09.06

일본도 2나노 공정 경쟁에 가세했다. 일본 정부의 지원을 받고 출범한 라피더스 연합도 2027년 2나노 공정 양산을 목표로 파운드리 사업을 준비 중이다. 라피더스는 토요타, 소니, 키옥시아, NTT, 소프트뱅크, NEC, 덴소, 미쓰비시UFJ은행 등 8개사가 2022년 11월에 설립한 반도체 회사다. 라피더스는 일본 북부 주요 섬인 홋카이도에 최첨단 반도체 공장을 건설 중이며, 미국 IBM과 협력해 2나노 공정 반도체 기술을 공동 개발하고 있다.

유재희 반도체공학회 부회장(홍익대 전자전기공학부 교수)은 "삼성의 GAA 기술의 신뢰성 및 고객 확보, 인텔-TSMC의 차세대 기술 협력, 일본과 미국의 협력 등 반도체 동맹의 향후 추이를 살펴볼 필요가 있다"라며 "기술적으로는 수율 및 가격, 다양한 니즈를 가진 고객에 대한 양질의 서비스, 반도체 생태계를 조성을 통한 턴키(turn key) 솔루션 공급 여부 등이 고객사 확보에 있어서 중요할 것"이라고 말했다.