글로벌 톱2 파운드리 기업인 삼성전자와 TSMC가 최근 첨단 패키징 분야로 기술 경쟁을 확대하고 있다. 반도체 회로 선폭을 좁히는 공정미세화가 한계에 봉착한 가운데 인공지능, 고성능 컴퓨팅 등 고성능을 요구하는 반도체 수요에 대응할 수 있는 기술로 첨단 패키지 기술이 주목받고 있기 때문이다.

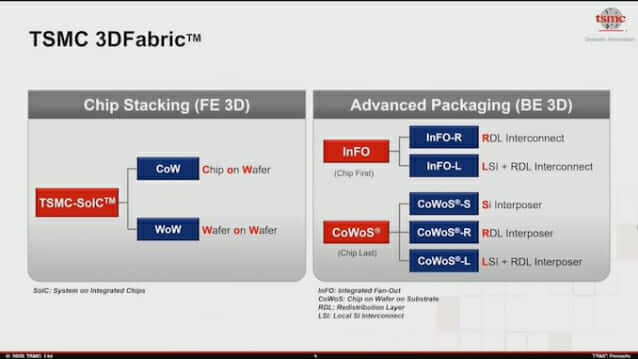

1일 대만 자유시보에 따르면 TSMC는 최근 애플을 주요 고객사로 확보하기 위해 첨단 3D 패키징 기술 '3D 패브릭 플랫폼'을 출시했다. TSMC의 3D 패브릭 플랫폼은 600마이크로미터 미만의 두께로 로직 반도체 위에 다수(약 12단)의 메모리 반도체를 적층할 수 있는 기술로, 내년 1분기 상용 서비스가 시작될 전망이다.

자유시보는 "TSMC가 선보인 3D 패브릭 플랫폼은 고급 패키징 시장을 장악하기 위한 것으로 시스템통합칩(SoIC), 칩온웨이퍼온서브스트레이트(CoWoS), 통합팬아웃(InFO) 등의 기술을 포함하고 있다"며 "이는 애플과 같은 주요 고객사로부터 고성능 컴퓨팅 및 인공지능에 대한 주문를 받기 위한 기술"이라고 전했다.

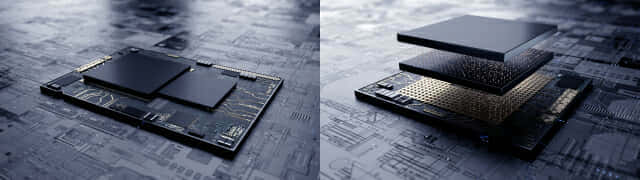

삼성전자도 지난 13일 첨단 3D 패키징 기술로 '엑스-큐브(X-Cube)'를 공개, 고급 패키징 시장 공략의지를 밝힌 바 있다. 삼성전자의 엑스-큐브는 전공정(반도체 제조)을 마친 웨이퍼 상태의 복수의 칩을 위로 얇게 적층해 하나의 반도체로 만드는 패키징 기술이다. TSMC의 3D 패브릭 플랫폼처럼 로직 반도체 위에 12단의 메모리 반도체를 적층할 수 있는 것으로 알려졌다.

특히, 삼성전자는 7나노미터(1nm=10억분의 1미터) 극자외선(EUV) 공정에서 생산된 반도체에 업계 최초로 3D 패키징 기술(엑스-큐브)를 적용하고, 이를 시험 생산하는 데 성공했다.

삼성전자 측은 "글로벌 팹리스 고객은 삼성전자가 제공하는 X-Cube 설계방법론과 설계툴을 활용해 EUV 기술 기반 5·7나노미터 공정 칩셋 개발을 바로 시작할 수 있다"며 "엑스-큐브는 슈퍼컴퓨터, 인공지능, 5G 등 고성능 시스템 반도체를 요구하는 분야는 물론 스마트폰과 웨어러블 기기의 경쟁력을 높일 수 있는 핵심 기술로 활용될 것"이라고 전했다.

시장에서는 삼성전자와 TSMC가 잇따라 첨단 3D 패키징 기술을 발표한 것을 두고, 양사가 고객사 확보전(戰)을 더욱 가속화할 것으로 보고 있다.

이는 3D 패키징 기술은 반도체를 수직으로 적층하는 방식으로 기존 2D 패키징 기술 대비 전체 칩 면적을 줄이면서 전력효율 등을 획기적으로 개선할 수 있기 때문이다. 더욱이 3D 패키징 서비스의 경우, 전공정부터 후공정까지 일원체계로 제공하는 방식인 만큼 애플 등의 대형 고객사를 확보하는 데 유리하다.

관련기사

- 삼성, EUV 적용 1z LPDDR5 D램 양산 시작2020.08.30

- 삼성, 美 IBM 차세대 CPU 만든다2020.08.17

- [단독] TSMC, 인텔 외장 그래픽칩 'Xe HPG' 위탁생산 '유력'2020.08.14

- EUV에 3D 적층 기술까지..삼성, 파운드리 초격차 강화2020.08.13

실제 TSMC는 지난 2017년과 2018년 통합팬아웃 패키징 기술을 앞세워 기존에 삼성전자와 나눠서 제조했던 애플의 애플리케이션 프로세서 물량을 독식한 바 있다.

한편, 시장조사업체 트렌드포스에 따르면 올해 3분기 글로벌 파운드리 시장에서 TSMC는 53.9%의 점유율로 1위를, 삼성전자는 17.4%의 점유율로 2위를 기록했다.