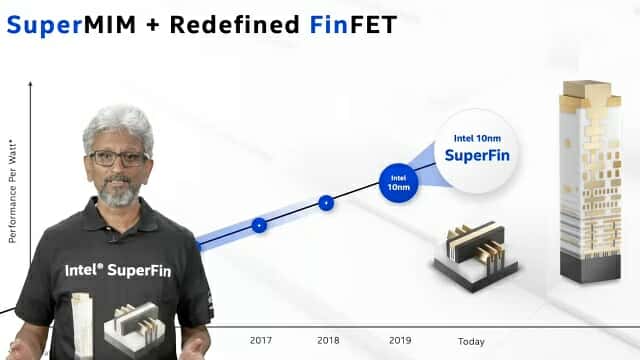

인텔이 11일(이하 미국 현지시간) 온라인으로 진행된 '인텔 아키텍처 데이' 행사를 통해 향후 출시될 프로세서에 적용될 새로운 트랜지스터 구조인 '슈퍼핀'(SuperFIN)을 공개했다.

슈퍼핀은 2011년부터 인텔이 프로세서에 적용해 온 3차원 구조인 핀펫을 개선해 작동 성능을 높여서 전력 효율을 끌어 올린 것이 특징이다.

인텔은 슈퍼핀 구조를 모바일(노트북)용 새 프로세서인 타이거레이크(Tiger Lake)를 시작으로 향후 출시될 새 프로세서에 지속적으로 투입할 예정이다. 또 오는 2021년에는 이를 더욱 발전시킨 구조인 인핸스드 슈퍼핀이 적용된다.

■ 2011년 이후 10여년 간 유지된 핀펫 구조

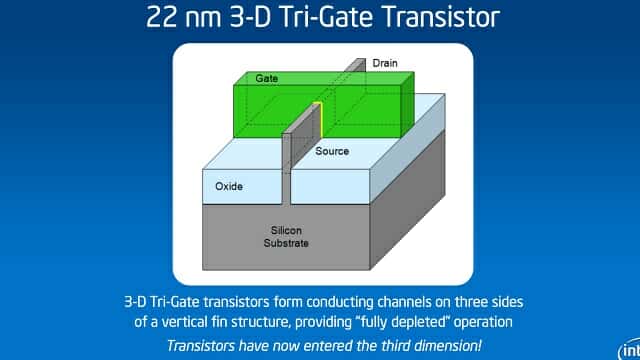

프로세서를 구성하는 트랜지스터는 게이트가 한쪽(소스)에서 다른 쪽(드레인)으로 흘러가는 전류를 제어하면서 0과 1을 반복해 껐다 켜며 작동한다. 그러나 20nm(나노미터) 등 프로세서 제조 공정이 미세해지면서 평면 구조의 트랜지스터는 전류가 새어나가는 등 부작용을 가져왔다.

인텔은 2011년 출시된 2세대 코어 프로세서(샌디브리지)부터 트라이게이트(Tri-Gate)라는 이름으로 3차원 트랜지스터 구조인 핀펫(FinFET)을 현재까지 적용해 왔다. 게이트를 지느러미 모양의 3차원 구조인 핀(Fin)으로 만들어서 누설 전류를 줄인 것이다.

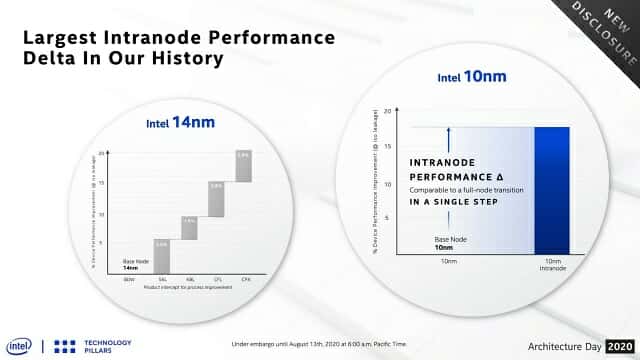

이후 인텔은 14nm, 10nm 공정에 이르기까지 핀펫 구조를 지속적으로 개선해 왔다. 또 지난 해 출시된 10nm 10세대 코어 프로세서(아이스레이크)에는 트랜지스터에 전류를 공급하는 인터커넥트에 코발트를 적용하면서 전류 공급을 원활하게 했다. 그러나 세대를 거치면서 보다 많은 트랜지스터를 집적해야 하는 상황에서 이는 근본적인 해결책이 되지 못했다.

■ 기존 10nm 공정 트랜지스터·인터커넥트 개선

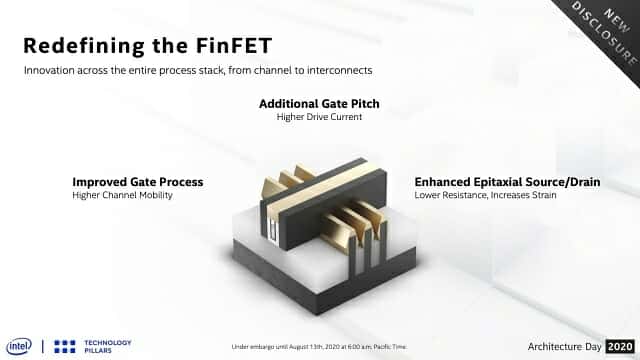

인텔이 공개한 슈퍼핀은 기존 10nm 공정을 그대로 유지하면서 트랜지스터, 또 트랜지스터를 제어하고 전원을 공급하는 인터커넥트를 개선해 전력 소모를 줄였다.

먼저 트랜지스터 소재의 저항 자체를 낮춰 전류가 보다 잘 흘러가게 했고 게이트에서 전류가 흘러가는 통로인 채널에 더 많은 전류가 빠르게 흐르도록 만들었다. 게이트를 통과하는 핀도 게이트와 다섯 개 면으로 맞닿게 해 전류 흐름을 보다 정밀하게 통제한다.

트랜지스터와 맞닿는 구리 배선을 감싸는 배리어 층도 얇게 만들어서 보다 많은 전류가 흐르게 했고 상층부에는 0.1nm 두께로 구성된 슈퍼 MIM 캐패시터를 적용해 전류가 잘 흐르게 만들었다.

■ 타이거레이크부터 순차적으로 슈퍼핀 적용

인텔이 공개한 슈퍼핀 구조는 7nm 공정 생산이 2021년 이후로 지연된 현재 상황에서 기존 10nm 공정을 최대한 활용하며 전력 소모와 트랜지스터 작동 속도를 높이기 위한 것이다.

실제로 인텔은 슈퍼핀 구조 적용을 통해 10nm에서 완전히 다른 공정으로 넘어 갔을 때와 같은 성과를 거뒀다고 설명하기도 했다.

이런 구조를 '슈퍼핀'이라고 부르는 이유에 대해 인텔 수석 부사장 라자 쿠드리는 "내부에서 공정 발전을 언급할 때 ' ' 기호를 덧붙여 왔지만 이런 방식이 혼동을 준다는 판단 아래 더 이상 이런 방식을 쓰지 않기로 했다"고 설명했다.

슈퍼핀 공정은 타이거레이크부터 적용되며 이를 더욱 개선한 '인핸스드 슈퍼핀' 공정은 내년에 출시될 서버용 프로세서에 적용될 예정이다.

■ 인텔 "포베로스 개선한 하이브리드 결합 연구중"

인텔은 트랜지스터 성능 향상을 위한 슈퍼핀 구조와 함께 서로 다른 공정에서 생산된 반도체를 연결하는 기술도 지속적으로 향상시킬 계획이다.

관련기사

- 하이브리드 아키텍처, PC 프로세서 새 돌파구 될까2020.08.11

- 인텔 '타이거 레이크' 내달 출시...노트북 시장에 바람 불까2020.08.05

- 'AI 엣지 컴퓨팅' 시대 여는 인텔 "파트너십이 곧 우리 비전"2020.07.29

- 파운드리 1위 노리는 삼성, 美 투자 나설까2020.07.27

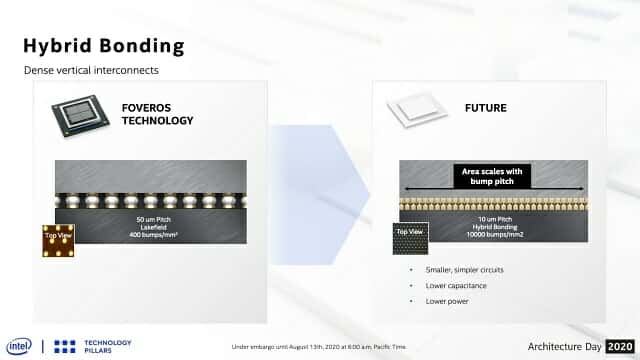

인텔은 2018년 말에는 프로세서와 메모리, 통신칩 등 서로 다른 공정에서 생산된 반도체를 수직으로 쌓아올리는 3차원 적층 구조인 포베로스(FOVEROS)를 공개했고 이를 적용한 첫 제품인 하이브리드 프로세서(개발명 레이크필드)를 올해 중순 출시했다.

하이브리드 결합 구조는 포베로스 구조를 더욱 발전시켜 반도체와 반도체 조각 사이 접점을 보다 조밀하게 배치하고 전력 소모를 줄일 수 있다. 인텔은 이 구조를 적용한 칩이 이미 지난 2분기부터 시범 생산에 들어갔다고 밝혔다.