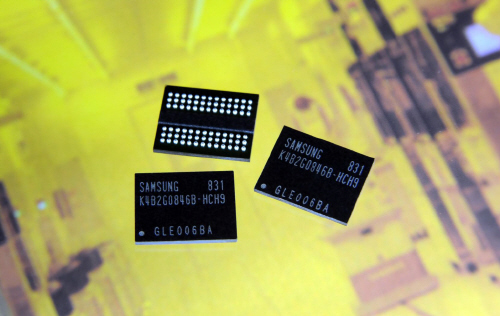

삼성전자가 세계 최초로 50나노급 공정을 적용한 2기가비트(Giga bit) DDR3 D램 개발에 성공, 10월부터 양산할 예정이라고 29일 공식 발표했다.

이에 따라 DDR2 제품이 주를 이루고 있던 고용량 D램 제품 시장을 DDR3 제품이 빠른 속도로 대체해 나갈 것으로 전망된다.

삼성에 따르면 50나노 2기가비트 DDR3는 2007년 삼성전자가 개발한 60나노 2기가비트 DDR2 D램의 최대 속도인 800Mbps(초당 800메가비트의 데이터 처리) 대비 약 1.6배인 1.333Gbps(1,333Mbps)를 구현하며, 단품 칩의 크기가 작아져 생산 효율도 기존 대비 60% 이상 향상됐다.

삼성은 이번에 개발한 2기가비트 D램 솔루션으로 고용량 DDR3 모듈을 양산할 예정으로 서버용 8기가바이트(Giga Byte) RDIMM, 워크스테이션 및 데스크톱PC용 4기가바이트(GB) UDIMM, 노트북용 4기가바이트(GB) SODIMM 등을 제작해 다양한 응용처에 대해 메모리 솔루션 용량 확대를 가속화할 예정이다.

기존 2기가비트 DDR2 D램 단품의 경우 칩 사이즈가 커서 고용량 모듈 제품을 만들기 위해서는 패키지 적층 기술(DDP: Double Die Package)을 적용, 2Gb 칩 2개를 하나로 만들어 탑재해왔다.

그러나 2기가비트 DDR3는 DDR2 D램 패키지 대비 대폭 축소되어, 적층 기술 없이 고용량 모듈 제작이 가능해 원가를 절감할 수 있다.

또한 1기가바이트 DDR3 D램 단품을 탑재한 현존 최고 용량 서버용 16기가바이트 DDR3 모듈의 경우는 1Gb DDR3 단품에 4단 적층(QDP: Quad Die Package) 기술을 적용해 원가 부담이 있었으나, 이번에 2기가 DDR3 D램이 출시됨으로써 2단 패키지 적층 기술(DDP)로 양산 예정이다.

2기가바이트 DDR3를 활용하면 공정과 원가 측면뿐만 아니라 전력 측면에 있어서도 큰 개선이 가능하다.

8기가바이트 D램 모듈의 경우, 기존 1기가비트 DDR3 D램 72개로 구성하던 것을 2기가비트 36개로 대체할 수 있기 때문에 40% 이상 전력을 절감할 수 있고, 이에 따라 시스템 작동時 발열량이 크게 줄어 신뢰성이 향상된다.

이처럼 2기가비트 DDR3 D램은 기존 DDR2 제품을 생산할 때 보다 단품 칩의 생산 효율을 60% 향상한 것 외에도 공정 단순화로 양산성이 증가되고 생산 기간도 단축되어 원가 경쟁력 우위를 확보할 수 있다.

또한 세트 제품에 탑재될 경우 전력 사용과 발열량을 감소시켜 최근 업계의 친 환경 특성 요구에도 더욱 경쟁력 있게 대응할 수 있다.

삼성전자는 “50나노급 2기가비트 DDR3 D램 출시를 계기로 PC 시장에서 프리미엄 서버 시장에 이르기까지, 향후 수년 이내 D램 시장의 주력 제품이 될 2기가 DDR3 제품군에서 확실한 주도권을 확보하게 됐다”고 밝혔다.

한편, 반도체 시장 조사기관인 IDC에 따르면 세계 DDR3 D램 시장은 Bit 기준으로 전체 D램 시장에서 '09년 29%, '11년 75% 규모로 성장하고, DDR3 D램 중 2기가비트 비중도 Bit(1Gb) 기준으로 각각 '09년 3%, '11년 33%를 차지할 것으로 전망했다.

※ 용어해설

◆RDIMM (Registered Dual In-line Memory Module)

- 기존 서버 및 워크스테이션 용으로 주로 사용되어 온 D램 모듈

- Control Signal을 위한 Register가 있는 메모리 모듈

◆UDIMM (Unbuffered DIMM)

- 데스크톱 PC용으로 주로 사용되어 온 D램 모듈

◆SODIMM (Small Outline Dual In-line Memory Module)

- Notebook등 소형 SET에 사용되는 메모리 모듈