플래쉬 메모리(flash memory)와 D램의 장점을 결합해 한 개의 메모리 트랜지스터에서 동작하는 차세대 퓨전 메모리 제품이 국내 연구진에 의해 개발됐다.

교육과학기술부는 카이스트(KAIST) 최양규(42세) 교수팀과 나노종합팹센터가 공동으로 기존 플래쉬 메모리와 D램이 한 개의 메모리 트랜지스터에서 복합기능을 수행함으로써 제작비용을 절감하고 집적도를 증대하는 차세대 퓨전메모리(URAM)을 개발했다고 14일 밝혔다.

U램(URAM)은 디지털 TV, 휴대용 정보기기 등의 발달에 따른 다기능•고성능화에 대응할 수 있는 차세대 퓨전메모리의 일종으로 이번 개발은 반도체 메모리분야의 원천기술과 실용성을 동시에 확보했다는데 의의가 있다.

기존의 퓨전 메모리는 D램, 플래쉬, S램 등의 서로 다른 칩을 차례로 쌓은 멀티칩 팩키지(MCP: multi chip package)형태로 단품 여러 개를 사용할 때보다 실장 면적을 줄이는 효과는 있지만 제작비용을 낮추기엔 한계가 있었다.

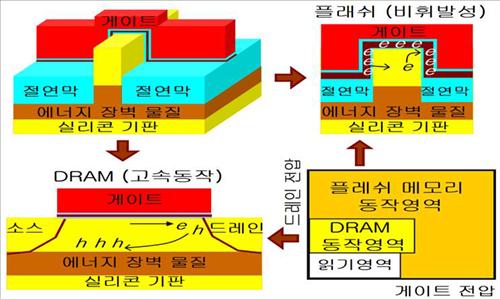

최교수팀은 D램과 플래쉬 메모리 동작전압 영역이 서로 다르다는 것에 착안해 트랜지스터의 몸통 안(floating body)에 전하를 모으고 지우는 과정을 통해 D램을 구현했으며, 그 몸통 위에 게이트 및 게이트 절연막으로 소노스(SONOS)구조를 결합시키는 방식으로 차세대 퓨전 메모리를 개발했다.

이번 연구결과에 적용된 3차원 나노구조 제작기술 및 소노스 절연막 형성기술은 현재 사용되고 있는 표준 반도체 설계 및 공정기술을 그대로 이용할 수 있기 때문에 반도체 업체는 개발기간 단축과 추가적인 비용투자 없이 제품 개발이 가능하다.

교육과학기술부는 PC 산업의 포화 등으로 기존 메모리 시장이 고수익을 내지 못하는 상황에서 이번 URAM의 개발은 기존의 메모리 기술을 진일보시킨 의미있는 연구결과로 평가받고 있으며, 이 제품이 2~3년내에 상용화될 경우 그 파급효과가 매우 크다고 할 수 있다.고 설명했다.

특히 퓨전 메모리 수요가 증가함에 따라 디지털 카메라•PDA•게임기•휴대폰 등에 U램 채택이 가속화 될 것으로 기대되며, 연구팀은 퓨전 메모리 시장 점유율이 전체 반도체 시장의 5%로 가정할 때 시장규모가 2010년 150억 달러, 2015년 204억 달러에 달할 것으로 전망하고 있다.

이번 연구 결과는 나노종합팹센터의 우수한 공정기술과 장비를 활용한 공동연구로 2007년 12월 12일 미국 워싱턴D.C.에서 개최된 국제전자소자학회(International Electron Device Meeting)에서 SOI 기판 위에 URAM 소자 개념이 처음으로 증명되었으며, 2008년 6월 17일 미국 하와이에서 열렸던 “초고집적회로 국제학회(Symposium on VLSI Technology)”에서 SiC 기판 위에 형성한 URAM 연구결과를 발표됐다. 현 U램과 관련된 국내특허 5건이 출원 중이다.

SONOS (Silicon Gate-Oxide-Nitride-Oxide-Silicon Channel) 기술이란:

높은 컨트롤 게이트전압으로 전하를 실리콘기판으로부터 상부의 얇은 산화막으로 터널링시켜 도체의 부유게이트에 저장시키는 기술적 문제들을 해결하기 위해 실리콘기판과 컨트롤 게이트 사이에 도체형 부유게이트 대신 산화막-질화막-산화막 (ONO) 의 부도체 층을 삽입하여 터널링된 전하가 질화막내의 전하저장장소 (트랩, Trap)에 저장되는 메커니즘을 이용한 전하트랩형 소자 기술이다. SONOS 기술을 이용하는 경우 전하가 저장되는 전하저장층의 두께를 10분의 1 수준으로 줄일 수 있으며 부도체를 전하저장층으로 사용함에 따라 인접한 메모리 소자간의 정보간섭 문제를 해결한 기술.