IBM이 비교적 새로운 칩 접속 기술을 이용해 성능 향상은 물론 전력소비도 줄일 수 있는 칩을 개발할 예정이라고 밝혔다.

일명 「TSV(through-silicon vias)」라는 이 기술은 별개의 부품, 즉 프로세서나 메모리, 또는 두 개의 개별 칩에 있는 코어들을 수천 개의 미세 와이어로 연결하여 데이터를 송수신하도록 하는 기술이다.

현재 칩의 데이터 전송은 대개 와이어로 구현된 버스(bus)라는 채널을 통해 이루어지는데, 데이터 전송 시 정체현상이 일어나기도 한다. TSV 기술을 이용하면 전력 소비를 줄이면서도 초당 데이터 전송률을 훨씬 더 높일 수 있다.

TSV란 기술을 처음 소개한 회사는 IBM이 아닌 인텔이지만, IBM은 이 기술을 상용화하는 최초의 회사가 될 전망이다.

IBM은 TSV가 적용된 통신용 칩 샘플을 올해 말 고객들에게 공개하고 2008년부터 칩 양산을 시작할 예정이다.

IBM이 선호하는 실리콘 게르마늄 칩에 TSV 기술을 적용할 경우 전력소비를 40% 가량 줄일 수 있을 것으로 예상된다. TSV는 칩에 미세한 구멍들을 뚫고 여기에 텅스텐을 채워 넣어 만들어지게 된다.

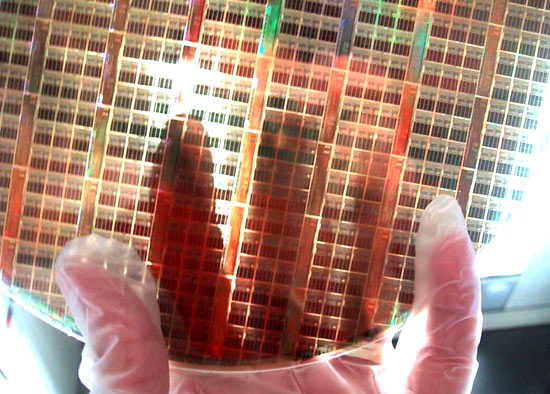

한 IBM 연구원이 일명 TSV(through-silicon vias) 기술을 사용해 결합될 웨이퍼를 손에 들고 있다. TSV란 데이터를 한 지점에서 다른 지점으로 전송하는 미세 연결부를 말한다. 우선 웨이퍼를 얇게 가공해 단일 패키지에 더 많은 수의 칩을 집적할 수 있도록 만든다. 그런 다음 실리콘에 미세한 구멍을 뚫고 여기에 금속(IBM 칩의 경우 텅스텐)을 채워 넣는다. 칩을 서로 결합시켜 레이어로 만들면 TSV가 완성된다. 이는 마치 땅콩버터 샌드위치 위에 빵을 하나 더 얹는 것과 같다.

IBM의 반도체 연구개발센터(Semiconductor Research and Development Center)의 리사 수(Lisa Su) 부소장은 와이어 결합은 잡음(noise) 수준이 매우 높은 편이어서 트랜지스터의 일정 부분에 성능 제한을 가져온다고 말했다.

앞으로 3-5년 이내에 TSV는 파워 프로세서와 메모리를 직접 결합하는데 사용될 수도 있을 것이다. 그렇게 되면 메모리 컨트롤러를 사용할 필요가 없어진다.

성능은 10%까지 향상시킬 수 있고 전력소비는 20% 정도 줄일 수 있다. IBM은 이 칩을 자사 슈퍼컴퓨터인 「블루진(BlueGene)」에도 적용했으면 하는 바람이다.

이와 더불어 TSV를 이용하면 칩을 수직 타워에 겹쳐 쌓을 수 있기 때문에 메인보드 공간도 효율적으로 활용할 수 있다.

현재 패키지 안에 칩을 수직으로 쌓는 방식을 이용하고 있는 칩 제조업체들이 몇 있지만 이들 칩은 버스를 통해 연결되는 것이 보통이기 때문에 공간 효율성은 어떨지 몰라도 대역폭만큼은 TSV를 따라갈 수 없다.

일반적으로 버스 포트는 칩의 측면에 위치한다. 하지만 TSV는 칩의 상부 또는 하부의 비교적 넓은 표면에서부터 뻗어 나와 실리콘으로 관통해 들어간다.

TSV를 적용한 칩 패키징에 의해 기존의 칩 판매 체계가 바뀔 가능성이 있다. 컴퓨터 제조업체는 프로세서나 메모리 또는 여타 통신용 칩을 서로 다른 벤더로부터 각각 구매하는 것이 아니라 「사전 연결된(prewired)」 칩들로 구성된 완성형 패키지를 구매하는 것이다.

따라서 IBM이나 인텔 등의 회사는 자신의 고급 반도체와 표준형 메모리를 패키지화함으로써 예전처럼 표준형 메모리를 다시 판매하게 될지도 모른다.

이 기술은 신종 프로세서처럼 헤드라인을 장식할 만한 특종은 아니지만 칩 상호연결 및 패키징 기술 분야는 근래 반도체 관련 혁신의 중심지가 되어왔다. 칩 설계자들이 이를 통해 반도체 성능의 현저한 향상을 이끌어 낼 수 있다고 믿기 때문이다.

샌디스크에 인수된 매트릭스 세미컨덕터(Matrix Semiconductor)라는 신생기업은 3D 메모리 칩 제조 방식을 개발했고 썬마이크로시스템즈는 칩들을 서로 보다 밀접하게 위치시켜 데이터를 교신하는 기술인「근접 커뮤니케이션(proximity communication)」기술을 연구 중이다.

한편 램버스는 초당 6.25 기가비트의 정보를 통과시키면서도 기가비트당 2.2 밀리와트라는 낮은 전력을 소비하는「칩-투-칩 인터커넥트(chip-to-chip interconnect: 칩간 상호연결)」기술인「로키(Loki)」를 개발했다.

램버스는 올해 초 로키의 참신성을 실제로 보여주기 위해 2개의 AA 배터리로 작동하는 디바이스를 하나 만들었다.

여기서 칩은 정지하기까지 40시간 이상 지속되었고 3.6 페타비트(petabit)의 데이터를 처리할 수 있었다. 이는 360만 기가비트, 혹은 3,600조 비트에 해당한다.

2005년부터 TSV 연구를 시작한 인텔은 지난 해 자사 개발자 포럼에서 TSV를 적용해 별개의 프로세서 코어에 메모리칩을 연결한 80 코어 칩을 선보였다.

래트너(Rattner)는 TSV를 두고 한 조각의 실리콘에 80개의 코어를 집적시키는 것보다 더 주목할 만한 성과라고 말하고 있다.

하지만 인텔은 지금까지 TSV 상용화를 위한 구체적 계획을 내놓지는 않았으며 단지 TSV를 적용해 칩을 양산하기까지 상당한 연구가 선행되어야 할 것이라고 언급했을 뿐이다.

문제는 프로세서가 메모리보다 더 많은 열을 발생시키기 때문에 이들을 패키지화하는 경우 난해한 열관리 기술이 요구된다는 점이다.

IBM은 이번 칩 개발을 통해 인텔을 일시적으로 따돌리는 데는 성공했다. 프로세서를 메모리에 연결하는 것은 통신용 칩에서 잡음을 줄이기 위해 TSV를 적용하는 것보다 난이도가 높은 작업이다.

수는 이번 칩 개발에서 무엇보다 혁신적이라 할 수 있는 점은 IBM이 극히 짧은 시간 내에 TSV 상용화의 발판을 마련했다는 점이라고 말했다.

올해 초 인터내셔널 솔리드 스테이트 서킷 컨퍼런스3(the International Solid State Circuits Conference3)에서 IBM은 TSV를 실험 중이라고 밝힌 바 있다. @