삼성전자·TSMC 등 주요 파운드리 기업들이 차세대 반도체 기술인 '실리콘 포토닉스' 상용화를 준비하고 있다. 이에 따라 관련 장비·소재 시장 역시 직접적인 변화를 맞을 전망으로, 후공정 영역에서는 '플럭스리스(Fluxless)' 기술이 특히 주목받고 있다.

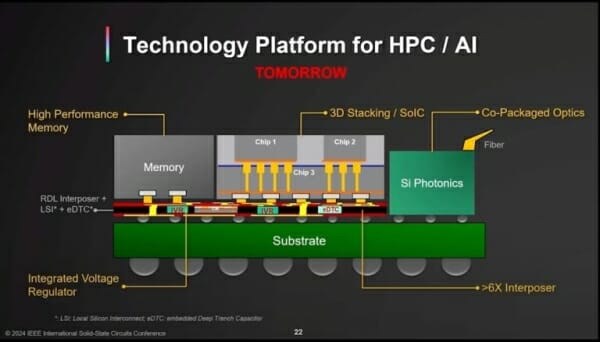

10일 업계에 따르면 주요 파운드리 기업들은 실리콘 포토닉스 기반의 '공동패키징형광학(Co-Packaged Optics, CPO)' 기술 상용화를 위한 연구개발(R&D)을 진행 중이다.

실리콘 포토닉스는 반도체의 신호 전달 방식을 전기에서 전자·빛으로 구현한 광자(Photon)로 바꾼 기술이다. 기존 대비 데이터 처리 속도 및 효율성 등을 크게 끌어올릴 수 있다.

CPO는 이 실리콘 포토닉스와 첨단 패키징 기술을 결합하는 개념이다. 실리콘 포토닉스 칩과 각종 반도체를 하나의 패키지 안에 통합해, 광 신호로 데이터를 주고받을 수 있게 만든다. 구리 배선을 활용하던 기존 패키징에 비해 AI 등 고성능 컴퓨팅 구현에 용이하다.

이에 TSMC와 삼성전자 등 주요 반도체 기업들도 CPO 기술의 도입을 준비 중이다. TSMC는 올해 자사의 최첨단 패키징에 CPO 기술을 접목한 샘플을 출시해, 이르면 하반기 본격적인 양산을 시작할 계획이다.

주요 고객사는 브로드컴, 엔비디아 등이 될 것으로 관측된다. 특히 엔비디아의 경우, 올 하반기 출시될 AI 가속기 'GB300'과 차세대 제품인 '루빈' 등에 CPO를 적용할 것으로 알려졌다.

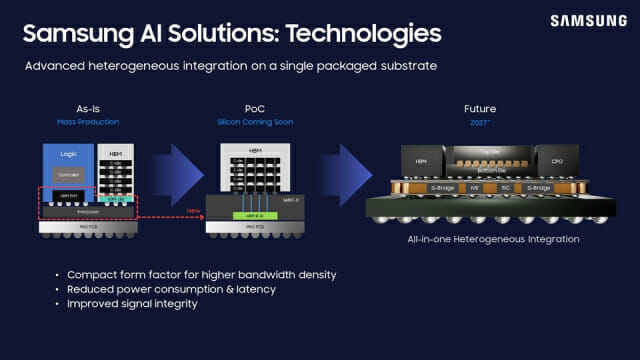

삼성전자 또한 오는 2027년 상용화를 목표로 CPO 기술을 개발하고 있다. 파운드리, 메모리, 패키징 등 각 사업부문별 역량을 집중해 턴키(Turn-Key) AI 반도체 솔루션을 공급하겠다는 구상이다.

반도체 업계 관계자는 "삼성전자가 파운드리 사업의 회복을 위해 CPO를 비롯해 여러 첨단 패키징 기술을 개발하고자 하는 의지가 높아졌다"며 "개발에 집중하기 위한 조직 개편 등도 고려하고 있는 것으로 안다"고 설명했다.

CPO 기술의 발전은 플럭스리스 본더 시장에 새로운 기회로 떠오르고 있다. 반도체 패키지 내부에는 칩과 기판을 연결해주는 무수한 범프(Bump)들이 존재한다. 기존에는 범프 부근의 산화막을 제거하기 위해 플럭스라는 소재를 사용했다. 반면 플럭스리스는 플럭스를 쓰지 않고 산화막을 제거하는 기술이다.

CPO에서 플럭스를 배제하려는 이유는 흄(Fume; 미세한 오염입자) 때문이다. 플럭스는 범프 접합 후에 말끔하게 세정돼야 하는데, 잔여물이 남게 되면 CPO 내 광통신을 방해하게 된다.

이에 세계 주요 반도체 장비 기업들은 CPO에 적용 가능한 플럭스리스 본더를 개발해 왔다. 일부 기업의 경우 미국 등 주요 시장에서 테스트를 테스트를 거치고 있는 것으로 알려졌다.

관련기사

- TSMC, CoWoS에 '플럭스리스 본딩' 적용 추진…AI칩 대형화에 대응2025.03.06

- 차세대 HBM용 본딩 고민하는 삼성전자, '플럭스리스' 평가 돌입2025.03.04

- "韓 고객사 관심 많다"…K&S, HBM4용 '플럭스리스' TC 본더 장비 파란 예고2025.02.23

- TSMC·인텔, 차세대 '실리콘 포토닉스' 공정 투자 고삐…삼성은 '신중'2023.10.17

다만 또다른 차세대 패키징 기술인 하이브리드 본딩도 CPO의 적용처로 거론되고 있어, 기술 개발 동향을 더 면밀히 살펴봐야 한다는 지적도 제기된다. 하이브리드 본딩이란 범프를 쓰지 않고 칩 혹은 웨이퍼의 구리 배선을 직접 붙이는 방식이다.

반도체 업계 관계자는 "실리콘 포토닉스에서는 기존처럼 플럭스를 쓸 수 없어, 향후 플럭스리스와 하이브리드 본딩이 경쟁하는 체제가 될 것"이라며 "하이브리드 본딩이 성능 향상에는 더 유리하나, 상용화를 위한 기술적 난제들이 아직 남아있어 향방을 더 지켜봐야할 것"이라고 설명했다.