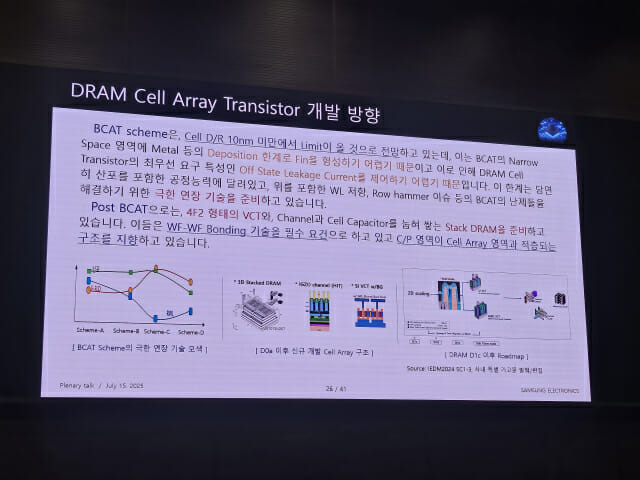

“BCAT 기반 기존 D램은 10nm(나노미터, 10억분의 1m) 미만에서 한계에 달할 것으로 전망됩니다.”

오정훈 삼성전자 마스터는 15일 소노캄 여수에서 진행 중인 ‘2025년도 반도체공학회 하계종합학술대회’에서 이같이 전망했다.

BCAT(Buried Channel Array Transistor)은 메모리 셀의 누설 전류를 줄이기 위해 개발된 트랜지스터 구조다. 채널 길이를 줄여 D램 셀의 크기를 줄이고 집적도를 높인다. 10나노 이하의 극미세 공정에서는 트랜지스터 크기를 줄여도 소자 간 간격이 좁아져 소자 간 연결을 위한 메탈의 저항이 커지고, 발열 문제가 발생할 수 있다.

오 마스터는 “셀 트랜지스터 공간을 다른 형태로 확장해서 써야한다”며 3D D램을 대안으로 제시했다.

3D D램은 메로리를 수직으로 쌓은 제품이다. 기존 D램은 셀이 수평으로 배치됐다. 기존 D램 대비 더 많은 셀을 집적할 수 있기 때문에 용량을 늘리고, 성능도 상승한다.

삼성전자는 3D D램 구현에 핀펫(FinFET) 공정을 적용한다. 핀펫은 반도체 소자의 성능 향상을 위해 개발된 3차원 구조 공정 기술이다. 평면(2D) 구조 한계를 극복하고 채널을 3면으로 둘러싼 게이트를 통해 전류 흐름을 효과적으로 제어한다. 과거 주로 파운드리(반도체 위탁생산)에 활용되던 기술이다.

오 마스터는 “컨벤셔널 D램에서도 핀펫을 전 제품에 쓰는 시대가 찾아올 것”이라고 말했다. 그러면서 “핀펫이 적용된 칩이 언젠가는 나오겠지만 시점에 대해서는 언급할 수 없다”며 “열심히 개발하고 있는 단계”라고 전했다.

다만 핀펫 공정은 페리 트랜지스터에만 적용된다. 페리는 D램에서 셀 주변의 회로를 제어하는 트랜지스터다.

관련기사

- 위로 쌓는 3D 반도체 시대 도래...핵심은 '극저온 식각'2025.07.14

- 삼성전자, DDR4 깜짝 수요 효과…2분기 실적 '가뭄에 단비'2025.06.11

- SK하이닉스, 10나노급 이하 D램 미래 기술 로드맵 공개2025.06.10

- 삼성전자 "1b·4F스퀘어 D램 사업 순항…메모리 초격차 유지할 것"2024.07.16

4F스퀘어 적용 여부에 대해서는 발표하지 않았다. 4F스퀘어는 현재 시장 주류 기술인 6F 스퀘어에서 셀 면적을 더 줄인 구조로, 집적도를 높일 수 있는 차세대 기술로 평가받는다. 그러나 삼성전자가 4F스퀘어를 기반으로 D램 구조를 바꾼 뒤, 3D D램을 개발한다는 점을 고려하면 4F스퀘어부터 핀펫 공정이 적용될 가능성이 크다.

그는 파운드리 기술이 메모리 공정으로 적용이 가속화되는 상황이냐는 질문에 “그렇다”고 긍정했다.