인텔이 9일(미국 현지시간)부터 오는 13일까지 미국 캘리포니아 주 샌프란시스코에서 진행되는 IEEE 국제전자소자학회(IEDM) 2023에서 반도체 전력 소모와 설계 복잡성을 줄일 수 있는 '반도체 후면 직접 접촉'(Backside Contact) 기술을 공개했다.

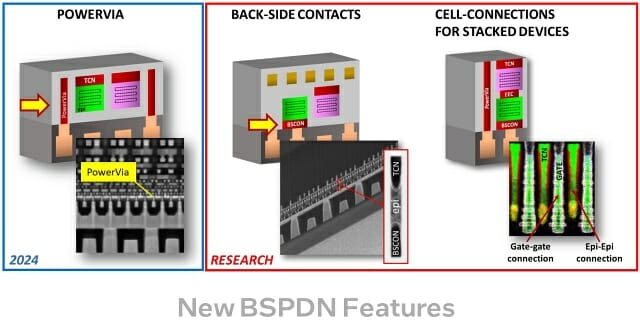

인텔은 2021년 트랜지스터 위쪽으로 각종 신호를, 트랜지스터 아래쪽으로 전력을 공급하는 배선 기술인 '파워비아'(PowerVia)를 공개한 데 이어 지난 6월 이를 적용한 시제품 '블루스카이 크릭'을 공개했다.

인텔이 이번에 공개하는 '반도체 후면 직접 접촉' 기술은 한 단계 더 나아가 전력을 필요로 하는 트랜지스터 소자에 반도체 다이 후면에서 직접 전력을 전달한다. 인텔은 "이 기술을 이용해 저전력 고성능 반도체를 실현할 수 있을 것"이라고 전망했다.

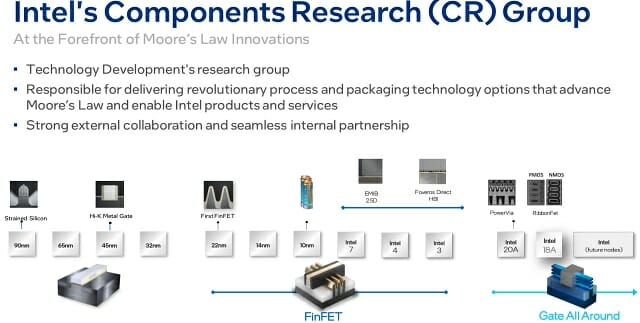

■ 컴포넌트 리서치 그룹, GAA 리본펫·포베로스 등 연구

인텔 컴포넌트 리서치 그룹은 전세계 반도체 관련 기업이나 학계와 협업해 인텔의 각 공정과 반도체 패키징에 필요한 기술을 선행 연구하는 조직이다.

컴포넌트 리서치 그룹이 관여한 기술에는 하이-K 메탈 게이트(45nm), 3차원 트랜지스터 구조 '핀펫'(22nm), 슈퍼핀 트랜지스터, 리본펫 등 프로세서 내 트랜지스터 구조와 수평 반도체 결합기술인 EMIB, 3차원 반도체 적층 기술 '포베로스' 등이 있다.

인텔이 2021년 7월 처음 공개한 반도체 후면 전력 공급 기술 '파워비아'와 IEDM 2023에서 공개하는 반도체 후면 직접 접촉 기술 역시 컴포넌트 리서치 그룹의 연구 결과물이다.

■ 금속층 거치지 않고 반도체 소자에 직접 전력 공급

내년 상용화를 앞둔 파워비아 기술은 반도체 내부에 전력과 신호를 공급하는 배선이 얽히며 복잡성을 더하던 문제를 해결하기 위해 등장했다. 트랜지스터 위쪽에서는 신호만 주고 받고 아래쪽에 전력을 공급하는 배선을 두는 것이다.

단 파워비아 기술은 트랜지스터에 직접 전력을 공급하는 것이 아니라 별도 금속층에 전력을 전달하는 방식이었다. '반도체 후면 직접 접속' 기술은 한 단계 더 나아가 반도체 소자에 직접 전력을 공급해 한층 더 단순화했다.

온라인 사전 브리핑에서 마우로 코브린스키 인텔 펠로우는 "이번에 공개한 기술은 금속 층을 줄이는 동시에 젼력 소모를 낮춘다. 또 반도체를 수직으로 쌓을 때도 활용해 전력 소모를 줄일 수 있다"고 설명했다.

이어 "이 기술이 상용화되면 트랜지스터를 보다 효율적으로 배치해 단위 면적당 집적도를 높이면서 고성능 저전력 반도체를 만들 수 있다"고 설명했다.

■ 파워비아·BSCon 이용한 CFET 2층 적층 기술 공개

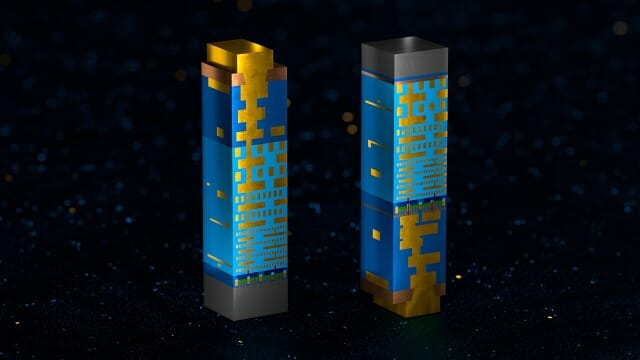

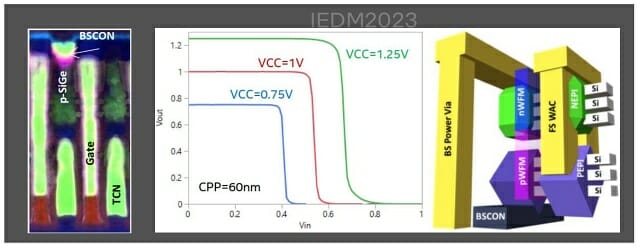

인텔은 IEDM 2023에서 파워비아와 반도체 후면 직접 접촉 기술을 이용해 상보형전계효과트랜지스터(CFET)를 수직으로 쌓는 기술도 공개했다.

CFET는 게이트 올어라운드(GAA) 트랜지스터 이후 더 미세화된 공정에 적용될 수 있는 새로운 트랜지스터 구조다. 인텔 뿐만 아니라 대만 TSMC 등도 2나노미터급 이하 공정 적용을 목표로 연구중이다.

인텔은 CFET를 수직으로 2층 쌓아 공간 효율성과 성능을 동시에 높인 새로운 구조를 공개했다. 트랜지스터 게이트와 게이트 사이 거리를 최대 60nm까지 줄이고 전력 공급 효율을 강화한 것이 특징이다.

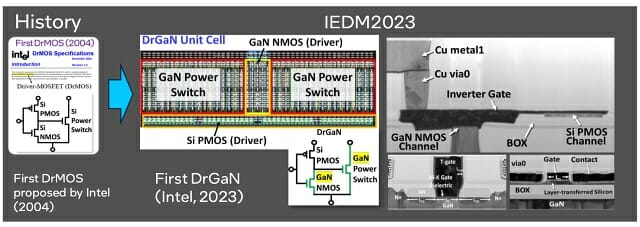

■ GaN 소자 실리콘 위에 직접 구현한 'DrGaN' 공개

인텔은 2021년 300mm 반도체 웨이퍼에 실리콘 기반 CMOS를 적용한 GaN(질화갈륨) 전원 스위치를 공개한 바 있다. 올해는 GaN 소자를 실리콘 위에 직접 구현한 'DrGaN'을 공개한다.

인텔 관계자는 "이 기술은 미래 컴퓨팅의 높은 전력 밀도 및 효율성 요구사항에 맞춰 전력 공급 솔루션을 구현할 잠재력을 지니고 있다"고 설명했다.

관련기사

- 파운드리 1나노 공정 경쟁 돌입...2030년 주류 전망2023.11.21

- PC용 Arm CPU 점유율, x86 CPU 반등에 소폭 감소2023.11.15

- "AI PC, 소프트웨어 없이 수요 창출 어렵다"2023.11.14

- 57.2조 축포 쏜 삼성전자, DX 재편·노조 파업 불확실성 직면2026.04.30

이어 "DrGan 기반 전력 반도체는 전기차, 스마트폰, 노트북 등 다양한 곳에 활용될 수 있을 것"이라고 덧붙였다.

이번에 인텔이 공개한 각종 신기술의 상용화 시점은 미정이다. 인텔 관계자는 "CFET 적층 등 기술은 아직 로드맵에 반영되지 않았으며 2025년 상용화 될 인텔 18A 이후에나 적용될 것"이라고 전망했다.