KAIST(총장 이광형)는 2진법과 3진법 논리를 전환해 가며 쓸 수 있는 반도체 회로를 개발했다고 11일 밝혔다. 데이터 처리 효율성과 집적도를 높일 수 있으리란 기대다.

3진법 논리 회로는 '0'과 '1', '2'의 3가지 논리 상태를 사용해 정보를 표현한다. 2진법 논리회로에 비해 같은 정보를 더 적은 논리로 표현할 수 있어 정보처리 효율성이 높다. 10진수 128을 2진법으로 나타내려면 8자리가 필요하지만, 3진법으로는 5자리만 필요하다. 반도체 칩을 더 작게 만들면서 처리 속도는 높이고 전력 소모는 줄일 수 있다.

하지만 논리 상태가 1개 더 추가됨에 따라 세 가지 논리 신호를 모두 안정적으로 출력하기 어렵고, 2진법과 3진법 논리 체계가 호환되지 않는 문제가 있어 상용화에 걸림돌이 됐다.

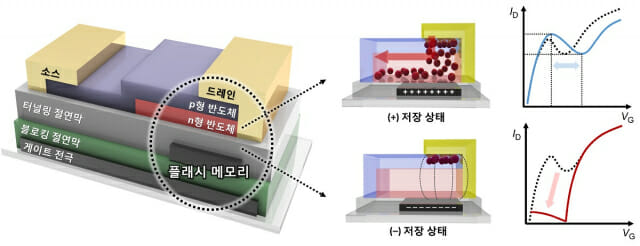

KAIST 생명화학공학과 임성갑 교수와 가천대 전자공학부 유호천 교수 공동연구팀은 3진법 논리 회로의 출력 특성을 회로 동작 중에 실시간으로 조절할 수 있는 새로운 논리소자를 개발했다. 3진법 논리 회로 자체에 정보를 저장할 수 있도록 회로를 구성하는 논리소자에 플래시 메모리를 집적했다. 플래시 메모리는 전원이 꺼져도 정보가 사라지지 않으며, 필요에 따라 정보를 저장하거나 다시 지울 수 있다.

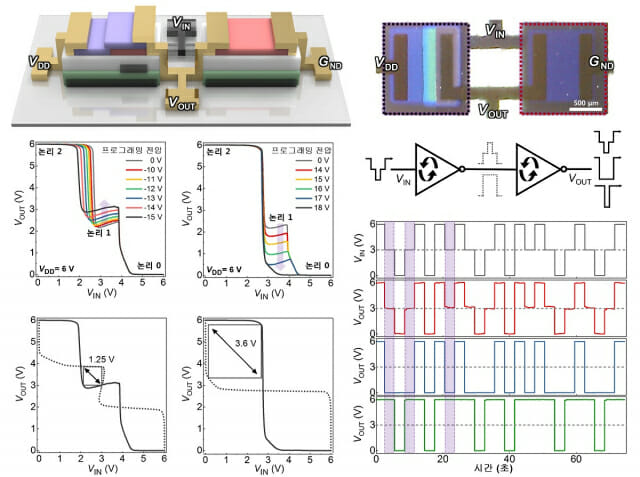

연구팀은 3진법 논리 회로가 저장하고 있는 정보에 따라 논리 상태 '1'의 출력 특성이 체계적으로 조절될 수 있음을 확인했다. 이를 통해 3진법 논리 회로의 동작 안정성(잡음 여유)을 세계 최고 수준인 60%까지 달성했다.

또 연구팀은 3진법 논리 회로에 저장된 정보를 완전히 지우는 경우에 논리 상태 '1'이 출력되지 않고 '0' 과 '2'의 두 논리 상태만 출력하는 점을 이용, 2진법과 3진법 논리 동작이 모두 가능한 회로를 구현했다. 논리 회로를 구성하는 각각의 논리소자에 서로 다른 정보를 저장하는 방식으로 2진법과 3진법 논리 출력을 조합했고, 이에 따라 다양한 종류의 논리 출력을 갖는 논리 회로를 구현함으로써 3진법 논리 회로의 정보 처리 효율 및 집적도를 향상시킬 수 있음도 확인했다.

이 논리소자는 같은 반도체 칩 안에서 2진법 논리 회로와 3진법 논리 회로를 연동해 데이터와 신호를 전달할 수 있다는 점에서 의의가 있다고 연구팀은 설명했다. 기존 2진법 체계를 유지하면서 필요에 따라 3진법의 높은 정보 처리 능력을 탄력적으로 활용할 수 있다. 향후 3진법 반도체의 상용화 시작 단계에 있어 핵심 기술이 될 것이란 기대다.

유호천 가천대 교수는 "이 연구는 논리 소자 안에 메모리 기능을 접목해 필요에 따라 2진법 연산과 3진법 연산이 자유자재로 전환이 가능한 혁신적 반도체 소자를 개발한 것"이라며 "기존 메모리 및 비메모리 칩 사이즈를 획기적으로 줄일 수 있는 유망한 기술이 될 것으로 기대한다"라고 밝혔다.

관련기사

- 이종호 장관 "기술 패권경쟁 시대, 반도체 중장기 지원 고민"2023.05.09

- 이재용이 콕 찍은 '차량용 반도체'...美서 고객사 확보 나선다2023.07.10

- "끝이 아니다"…SK·두산, 반도체 패키징 추가 M&A 후보 물색2023.07.10

- 57.2조 축포 쏜 삼성전자, DX 재편·노조 파업 불확실성 직면2026.04.30

임성갑 KAIST 교수는 "기존 디지털 논리 회로와 비교해 다양한 연산이 가능하고 복잡한 연산을 훨씬 단순화할 수 있는 논리소자를 개발한 것"이라며 "향후 대용량 정보 처리가 필요한 인공지능, 사물인터넷 등 다양한 분야를 위한 신개념 반도체 소자에 있어 유용한 지침이 될 것으로 기대된다"라라고 말했다.

이 연구는 선도연구센터 지원사업(웨어러블 플랫폼 소재 기술센터), 이공분야기초연구사업(과학기술정보통신부), 산업기술혁신사업(산업통상자원부)의 지원을 받아 수행됐으며, 학술지 '네이처 커뮤니케이션 (Nature Communications)'에 최근 게재됐다. 논문 제목은 A reconfigurable binary/ternary logic conversion-in-memory based on drain-aligned floating-gate heterojunction transistors이다.