더 강력한 칩을 만들려면 어떻게 해야 할까? HP의 새 제안서에 따르면 원자재를 줄이면 된다고 한다.

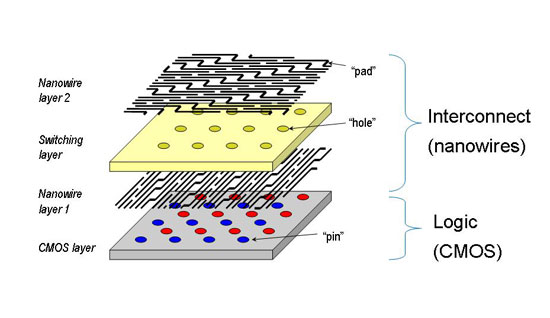

이번달 HP 랩스(Labs)의 연구자들은 특정한 종류의 칩에 대한 성능을 상당히 증가시키고 전력 소모량을 줄일 수 있는 방법에 관해 약술한 논문을 발표할 예정이다. 그 방법이란 칩 내부의 통신 와이어를 작은 나노 와이어로 구성된 오버헤드 그리드로 대체하는 것.

이 아키텍처 컨셉은 반도체 설계자들이 직면하고 있는 주된 문제들 중 하나를 해결하는데 도움이 되는 신선한 방법으로 증명될 수 있다. 그 문제는 칩과 칩 안의 부품을 계속 축소시키는 방법에 관한 것이다.

무어의 법칙에서 설명한 것처럼 칩 제조업체들은 2년마다 한 번씩 트랜지스터와 인터커넥트(interconnect:트랜지스터를 연결하는 금속 와이어)의 크기를 줄이는 방법으로 성능을 증폭시키고 생산 비용을 절감할 수 있었다.

하지만 부품 크기를 줄이는 일은 점점 더 어려워지고 비용이 많이 들고 있다. 그 결과 설계자들은 성능이나 에너지 효율성 및 비용 사이에서 절충하지 않을 수 없었다.

스탠 윌리엄스(Stan Williams)는 하지만 크로스바(crossbar) 구조로 전환하면 크기 축소 공식이 근본적으로 바뀔 것이라고 말했다. 스탠 윌리엄스는 HP의 선임 직원이며 HP 랩의 양자 과학 연구(Quantum Science Research) 팀 담당 이사.

기존 인터커넥트를 제거하면 당연히 칩의 크기가 엄청나게 줄어든다. 성능은 증가하지만 칩은 기존 트랜지스터로 만들 수 있다. 이상적이게도 비용 또한 줄어든다. 이 기술의 경우 새로운 반도체 제조 장비에 수십억 달러를 투자할 필요가 없기 때문. 동시에 전력 소모량이 줄어들 가능성도 있다.

윌리엄스는 인터뷰에서 사람들은 무어의 법칙이 깨지길 손꼽아 기다렸지만 토론된 많은 내용을 통해 이런 트랜지스터를 더 이상 줄이는 일이 너무 어렵다는 것을 알았다고 밝히고 여기에서 문제는 트랜지스터를 축소시키지 않고도 칩 밀도를 높이고 전력 소모량을 줄이며 작동 속도를 높일 수 있다는 것을 원칙적으로 (적어도 한 종류의 칩에서는) 증명했다는 것이라고 말했다.

크로스바

크로스바는 지난 몇 년 동안 HP 랩에서 나온 꽤 주목할 만한 아이디어 중 하나. 이 회사는 이 구조를 이용해 메모리칩을 향상시키고 제조 결함을 보정하여 회로의 계산 능력을 개선하는 방법을 보여주었다.

HP가 칩 업계를 크게 흥분시킨 건 사실이지만 전통적으로 HP는 기술 라이선스 사업으로 수입을 올리는 일을 더 중시한다. 크로스바 컨셉이 실제로 이용된다면 HP는 로열티로 수백만 달러를 벌어 들일 수 있을 것이다.

윌리엄스는 “HP가 지금까지는 크로스바 그리드를 사용해 FPGA(field-programmable gate array:이미 설계된 하드웨어를 반도체로 생산하기 직전 최종적으로 하드웨어의 동작 및 성능을 검증하기 위해 제작하는 중간 개발물 형태의 집적 회로) 시뮬레이션을 만든 정도이고 올해 말까지는 프로토타입을 만들고 싶어한다”고 말했다.

2010년까지 제조업체들은 크로스바 통신 시스템을 상용 칩에 내장시킬 수 있을 것이다.

궁극적으로 이 컨셉을 다른 종류의 칩에 내장시키는 일도 가능할 것이다. 많은 분석가들은 1990년대에 알루미늄을 밀어낸 구리 인터커넥트가 반대로 밀려나게 될 것이라고 이미 예언한 바 있다.

윌리엄스와 HP의 그레그 스나이더(Greg Snider)는 다양한 다수의 기능에 맞게 프로그램 할 수 있는 칩인 FPGA로 이 컨셉을 연구하고 있다. 부분적으로는 이 분야에서 가장 큰 이득을 얻을 수 있을 것이기 때문. FPGA에서는 서로 다른 종류의 기능 블록이 인터커넥트를 통해 서로 직접 연결돼 있다. 마치 구식 인터콤 시스템과 비슷하다.

그렇기 때문에 FPGA의 기능 블록이 증가하면 데이터 경로의 수가 기하급수적으로 증가한다. 윌리엄스는 FPGA에서 모든 통신 원자재는 칩 영역의 80%까지도 차지할 수 있다”고 말했다.

크로스바 시스템은 연결할 필요가 있을 때에만 기능 블록을 연결하는 지능형 통신 시스템을 사용하기 때문에 기존 칩의 정적 배선 방식이 사라진다 (HP 랩에서 수행하는 프로젝트 중 일부는 뉴욕의 스토니 브룩대학교(Stony Brook University)에서 과거에 수행했던 연구에 기초한 것이다).

크기 문제

잠재적인 이득은 무수히 많다. 동적 통신 네트워크의 경우 특정한 기능 블록이나 트랜지스터 영역은 사용하지 않을 때 슬립 상태가 되므로 전력 사용이 줄어든다. 제조업자들은 결함이 있는 회로를 우회하여 문제가 있는 멀티코어 칩을 구제할 수도 있다.

윌리엄스는 불량 트랜지스터 하나 때문에 제품을 쓰레기 더미에 집어 넣을 필요는 없다”고 말했다.

HP는 45㎚ 트랜지스터와 길이가 4.5㎚인 나노와이어 그리드로 만든 FPGA가 45㎚ 프로세스에서 만든 표준 FPGA에 비해 크기가 4% 정도 밖에는 안 될 것으로 추정했다(그 45㎚ 프로세스에서 만든 칩은 올해 말에 나올 예정. ㎚ 척도는 칩의 평균 요소 크기를 가리킨다. ㎚는 1m의 10억분의 1).

가설에 따르면 칩의 클럭 속도는 더 느리지만 계산당 소모되는 에너지 양은 더 낮아진다고 한다.

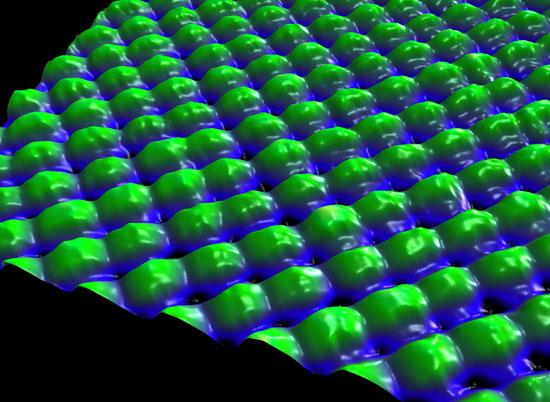

크로스바 구조 자체는 요즘의 인터커넥트보다 더 작은 알루미늄이나 구리 나노와이어로 만들 수 있다. 크기를 줄이는 문제도 임프린트 리토그라피(imprint lithography)라는 새로운 프로세스를 채택해 처리할 수 있다.

전통적인 리토그라피에서는 광 빔을 사용해 실리콘의 트렌치(trench)를 ‘끌어당긴다(draw)’ 그러면 트렌치가 화학적 프로세스를 거쳐 빠져 나온 후 알루미늄으로 채워진다. 임프린트 리토그라피란 의미하는 그대로 즉, 몰드를 처리된 실리콘에 밀어 넣은 후 그 결과 만들어진 임프린트가 금속으로 채워지는 것.

임프린트는 기존 리토그라피에 비해 생성되는 라인 수가 적지만 아직까지는 대규모로 채택되지 않았다. 이 기법은 회로 라인이 상당히 규칙적일 때 가장 잘 작동하며 HP의 크로스바 프로젝트와 연계돼 있다. 즉 크로스바 그리드는 90도 각도로 두 레이어의 병렬 와이어로써 구성된다.

하드 드라이브 제조사들은 미래의 하드 드라이브 미디어에서 패턴을 만드는데 임프린트 기법을 사용하는 것을 고려하고 있다.

이 논문은 24일자(미국시간) 나노테크놀로지(Nanotechnology)에 기재될 예정이며 HP는 그로 인해 상당한 파문이 일어나기를 기대하고 있다.

윌리엄스는 이것에 대해 “상당히 커다란 일(Big deal)이라고 생각하고 있다”고 전했다. @